Altera 100G Interlaken MegaCore Function User Manual

Page 39

You must enforce the following additional constraints in sending dual segment traffic to the TX user data

transfer interface:

• The application can start a packet or burst transfer in a single cycle on only one of the most significant

byte (Byte 63) or the middle position (Byte 31) in the 512-bit data symbol. Therefore, the application

can assert only one of

itx_sop[1]

and

itx_sop[0]

, and only one of

itx_sob[1]

and

itx_sob[0]

, in

a given cycle. This constraint ensures that the minimum number of idle and data bytes between

consecutive starts of packet or burst is at least 64.

• The application can end a packet or burst transfer only once in a single cycle. Therefore, the minimum

number of idle and data bytes between consecutive ends of packet or burst must be at least 64.

The same constraints apply to dual segment traffic on the RX user data transfer interface: the minimum

number of idle and data bytes between consecutive starts of packet or burst must be at least 64, and the

minimum number of idle and data bytes between consecutive ends of packet or burst must be at least 64.

The 100G Interlaken IP core enforces these constraints on the RX user data transfer interface.

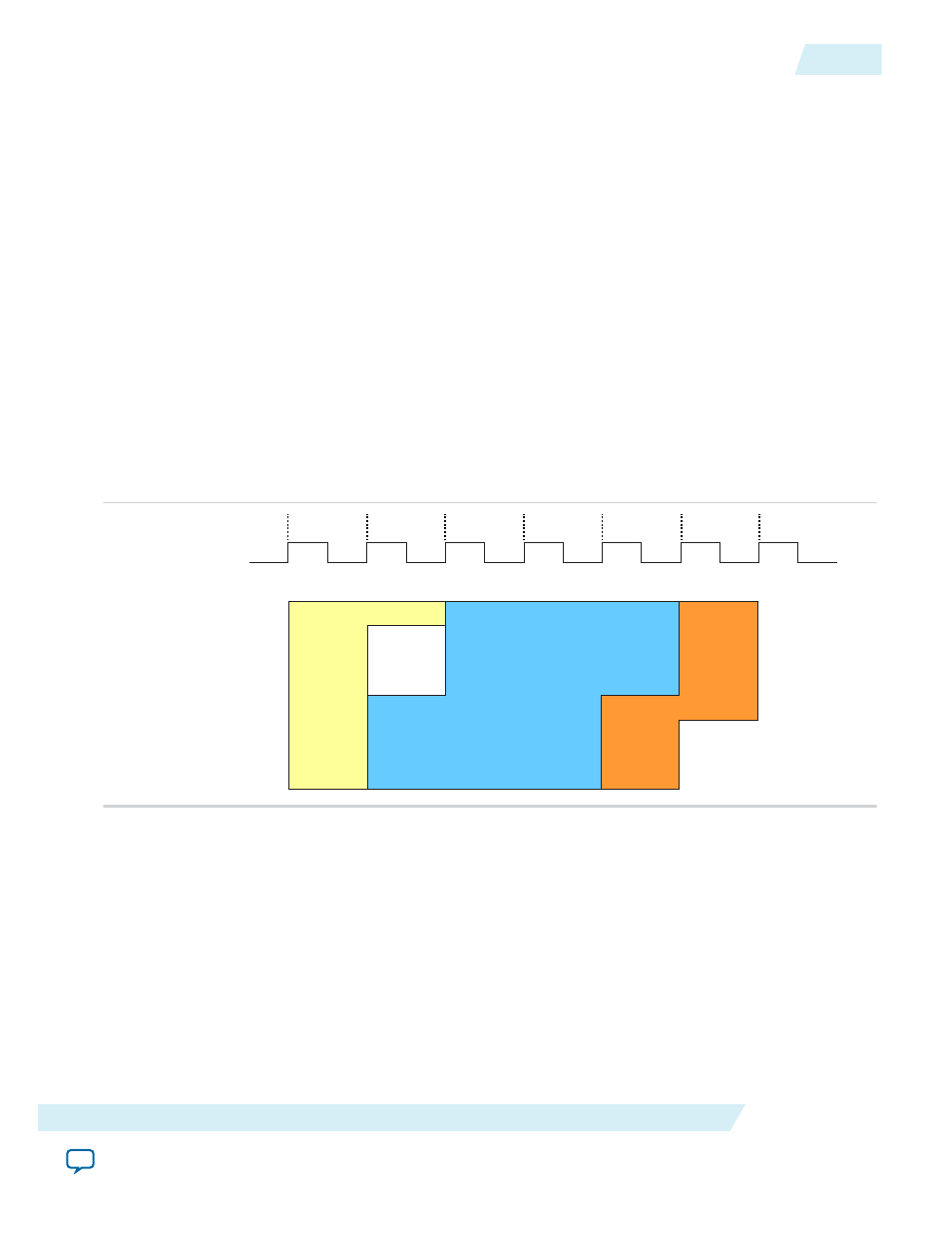

Figure 4-4: Dual Segment Data Transfer

In a dual segment data transfer, the end of one data burst and the start of another can appear in the same

clock cycle. In this example, each column represents a single 512-bit data symbol, divided into 64-bit

words, and each color represents a separate data burst. The second and third data bursts are dual segment

transfers.

Word 7 (bits [511:448])

Word 6 (bits [447:384])

Word 5 (bits [383:320])

Word 4 (bits [319:256])

Word 3 (bits [255:192])

Word 2 (bits [191:128])

Word 1 (bits [127:64])

Word 0 (bits [63:0])

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 5

Cycle 6

Cycle 7

dw8

dw0

dw1

dw2

dw3

dw0

dw1

dw2

dw3

dw4

dw5

dw6

dw7

dw4

dw5

dw6

dw7

dw8

dw9

dw10

dw11

dw12

dw13

dw14

dw15

dw16

dw17

dw18

dw19

dw20

dw21

dw22

dw23

dw0

dw1

dw2

dw3

dw4

dw5

dw6

dw7

dw8

Eight-word data symbol::

Related Information

•

•

100G Interlaken IP Core User Data Transfer Interface Signals

•

100G Interlaken IP Core Dual Segment Interleaved Data Transfer Transmit Example

15

Example of dual segment data transfers on the TX user data transfer interface.

•

100G Interlaken IP Core Dual Segment Interleaved Data Transfer Receive Example

on page 4-22

Example of dual segment data transfers on the RX user data transfer interface.

UG-01128

2015.05.04

Dual Segment Mode

4-9

Functional Description

Altera Corporation