I/o standards – Altera PHYLite User Manual

Page 11

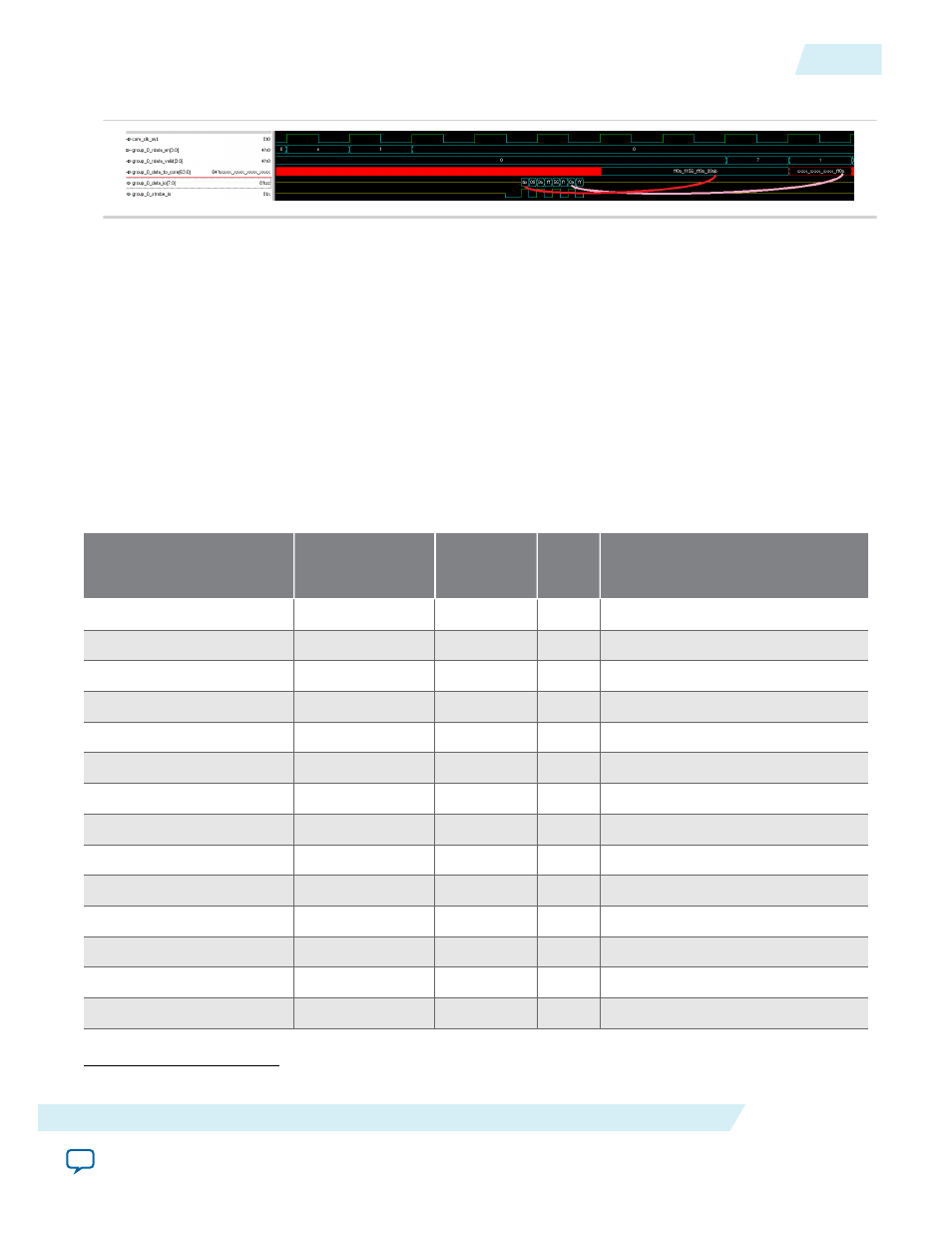

Figure 12: Example Input (Quarter Rate DDR) - Unaligned

I/O Standards

The Altera PHYLite for Parallel Interfaces IP core allows you to set I/O standards on the pins associated

with the generated configuration. The I/O standard controls the available strobe configurations and OCT

settings for all groups.

When you select an I/O standard in the I/O standard parameter, the reference clock assigns the I/O

standard as a single-ended input. For a differential reference clock, override the single-ended Quartus II

IP File (.qip) setting in the .qsf.

If you want to assign I/O standards manually at the system level (in the .qsf), then set the I/O standard to

none

, which will not output any I/O standard related .qip assignments from the IP generation.

Table 5: I/O Standards

I/O Standard

Valid Input

Terminations (Ω)

(1)

Valid Output

Terminations

(Ω)

(1)

RZQ

(Ω)

Differential/Complementary I/O

Support

SSTL-12

60, 120

40, 60

240

Yes

SSTL-125

20, 30, 40, 60, 120

34, 40

240

Yes

SSTL-135

20, 30, 40, 60, 120

34, 40

240

Yes

SSTL-15

20, 30, 40, 60, 120

34, 40

240

Yes

SSTL-15 Class I

0, 50

0, 50

100

Yes

SSTL-15 Class II

0, 50

0, 25

100

Yes

SSTL-18 Class I

0, 50

0, 50

100

Yes

SSTL-18 Class II

0, 50

0, 25

100

Yes

1.2-V HSTL Class I

0, 50

0, 50

100

Yes

1.2-V HSTL Class II

0, 50

0, 25

100

Yes

1.5-V HSTL Class I

0, 50

0, 50

100

Yes

1.5-V HSTL Class II

0, 50

0, 25

100

Yes

1.8-V HSTL Class I

0, 50

0, 50

100

Yes

1.8-V HSTL Class II

0, 50

0, 25

100

Yes

(1)

0 is equivalent to none.

ug_altera_phylite

2015.01.16

I/O Standards

11

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation