Altera PHYLite User Manual

Page 51

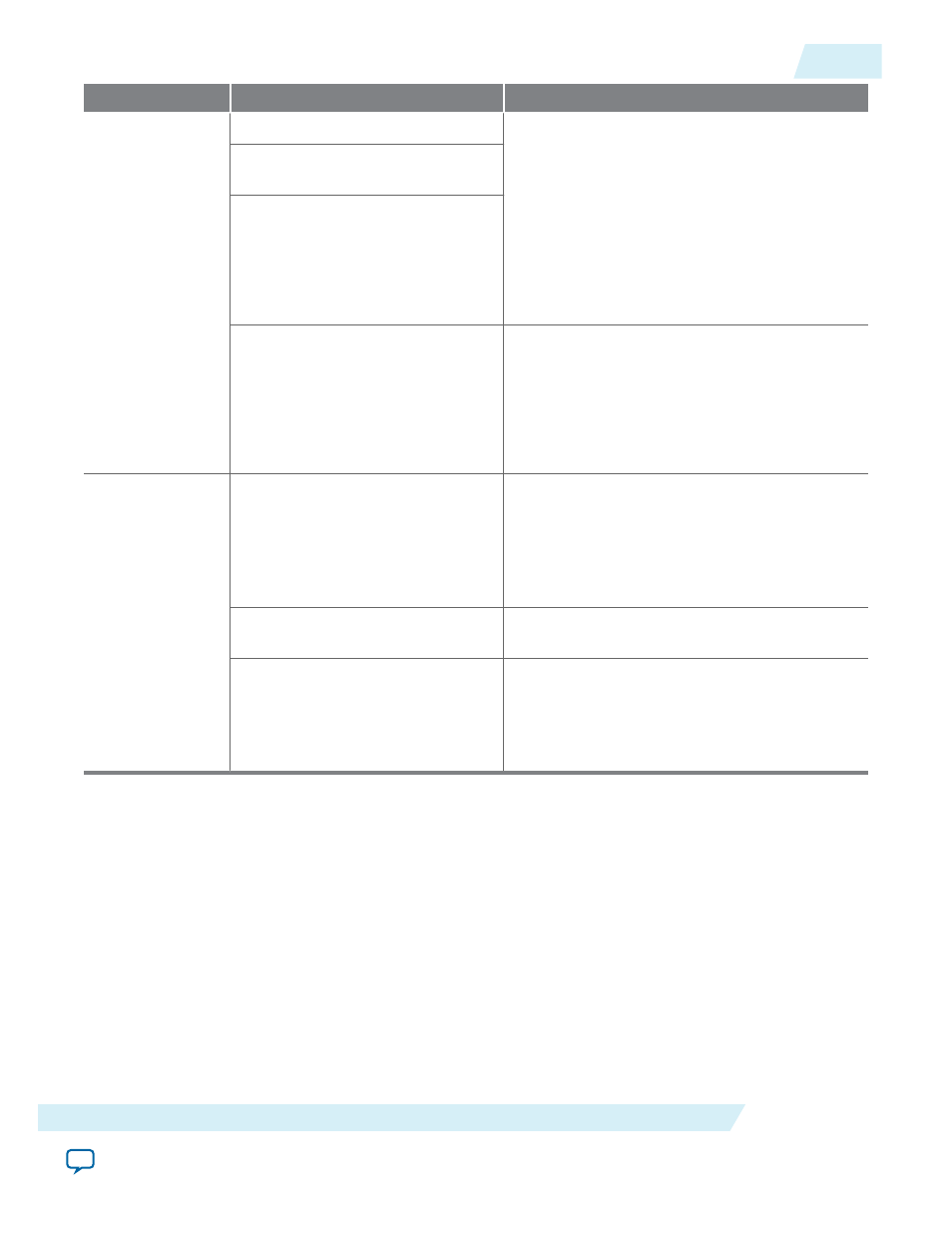

Section

Parameter

Description

Capture Strobe

Use capture strobe enable block

You cannot access the capture strobe in the

Altera PHYLite for Parallel Interfaces IP core

because the DQS enable control is an internal

block controlled by the read/write latency

settings.

In Arria 10 devices, the capture strobe enable

block is used for input/bidirectional applica‐

tions. It is controlled by the group's

rdata_en

input port and read latency settings.

Treat the capture strobe enable as

a half-rate signal

DQS enable phase setting

Use inverted capture strobe

This feature is necessary for QDR protocols.

This parameter is only available for Arria V and

Cyclone V devices.

The Swap capture strobe polarity parameter is

available for complementary strobe configura‐

tions.

Output Strobe

Use reset signal to stop output strobe There is a reset pin generated in ALTERA_

PHYlite instantiation, except that it is for the

entire ALTERA_PHYlite reset, rather than

allowing stopping of the uni-directional output

strobe using this parameter in the ALTDQ_

DQS2 IP core.

OCT source

The OCTs in Arria 10 devices are built-in. You

do not need to manually instantiate the OCTs.

Preamble type

This option is not necessary in the Altera

PHYLite for Parallel Interfaces IP core because

you can control and customize the output

strobe pattern from the core logic using

group_

x_strobe_out_in

signal.

Example Design: Manual IP Migration from ALTDQ_DQS2 IP Core to the Altera

PHYLite for Parallel Interfaces IP Core

This example design demonstrates how to migrate from the ALTDQ_DQS2 IP core to the Altera PHYLite

for Parallel Interfaces IP core on a simple PHY-only design targeting external NAND Flash device. This

example design targets a Stratix V device. In Arria V, Cyclone V, and Stratix V devices, a PHY system

design that uses the ALTDQ_DQS2 IP core requires other IP cores such as the ALTERA_PLL, ALTDLL,

and ALTOCT IP cores.

Note: A proper NAND Flash external memory interface does not require any OCT. However, for general

migration illustration purposes, ALTOCT is instantiated in this example design.

ug_altera_phylite

2015.01.16

Example Design: Manual IP Migration from ALTDQ_DQS2 IP Core to the Altera

PHYLite for Parallel Interfaces IP Core

51

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation