Dynamic reconfiguration example design, Ip migration for arria v, cyclone v, and stratix v – Altera PHYLite User Manual

Page 44

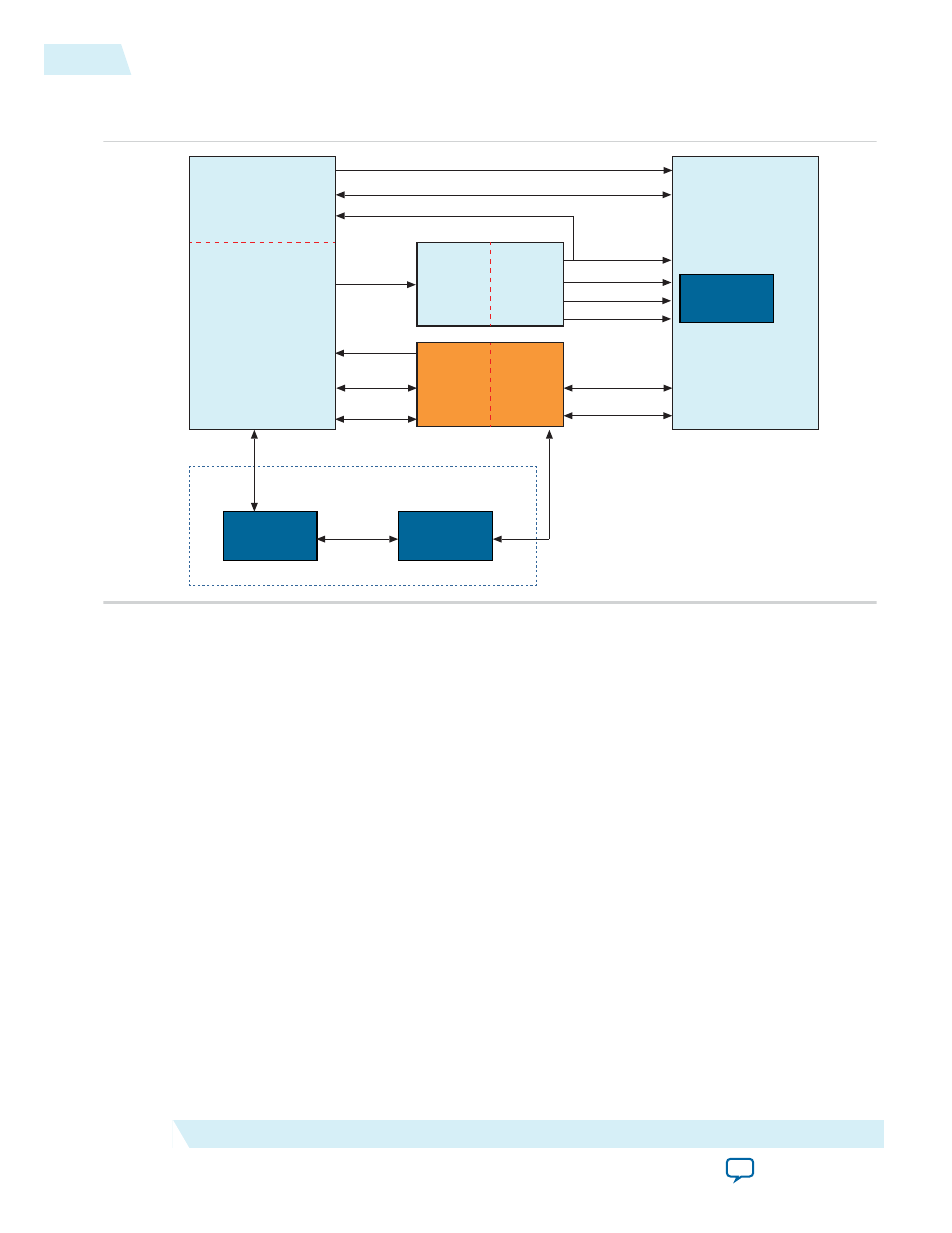

Figure 19: High-Level View of the Simulation Example Design with One Group

This figure shows a high-level view of the simulation example design with one group.

Side read/write command

Side read/write data

DRAM clock

Write command

Read command

Agent select

data

strobe

data

sim_ctrl

DRAM clock

Latency Delays

DRAM clock

Core clock

PHYLite DUT

PHYLite ADDR/CMD

DRAM clock

Core clock

Read/Write

command

Core clock

Read/Write

enable

DRAM clock

Core clock

Agent (one per group

in DUT)

cfg_ctrl

avl_ctrl

Avalon Bus

Dynamic Reconfiguration Only

Reconfiguration

Flow Control

Avalon Bus

Dynamic Reconfiguration Example Design

When you select the dynamic reconfiguration option, the example design introduces the

cfg_ctrl

and

avl_ctrl

blocks, which work with the

sim_ctrl

module to demonstrate the basic functionality of the

Altera PHYLite IPs Avalon-MM based reconfiguration. The agent is also modified to insert delays on the

data and clocks, which the new modules will compensate for.

Before sending test data, the

sim_ctrl

module first asks the

cfg_ctrl

to sweep for working delay values.

While sweeping over the values, the

cfg_ctrl

module requests the

sim_ctrl

to perform writes and reads

and return the results. The setting of the delays is simplified by the

avl_ctrl

module, which is described

in detail in

Example Design Avalon Controller

on page 29.

NOTE: The

cfg_ctrl

module performs a simplistic reconfiguration of the interface that stops at the first

working delay values. This works in simulation but will likely fail in a hardware scenario, as the initial

working delay will be marginal. A robust calibration algorithm should sweep over the entire valid range of

delays to choose the correct value for the application.

IP Migration for Arria V, Cyclone V, and Stratix V

In Arria 10 devices, you can instantiate the Altera PHYLite for Parallel Interfaces IP core on its own

because the IP core contains the OCT and PLL. However, in Arria V, Cyclone V, and Stratix V devices,

you must instantiate the ALTDQ_DQS2 IP core with the ALTERA_PLL, ALTDLL and ALTOCT IP cores.

44

Dynamic Reconfiguration Example Design

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide