Input path signals – Altera PHYLite User Manual

Page 40

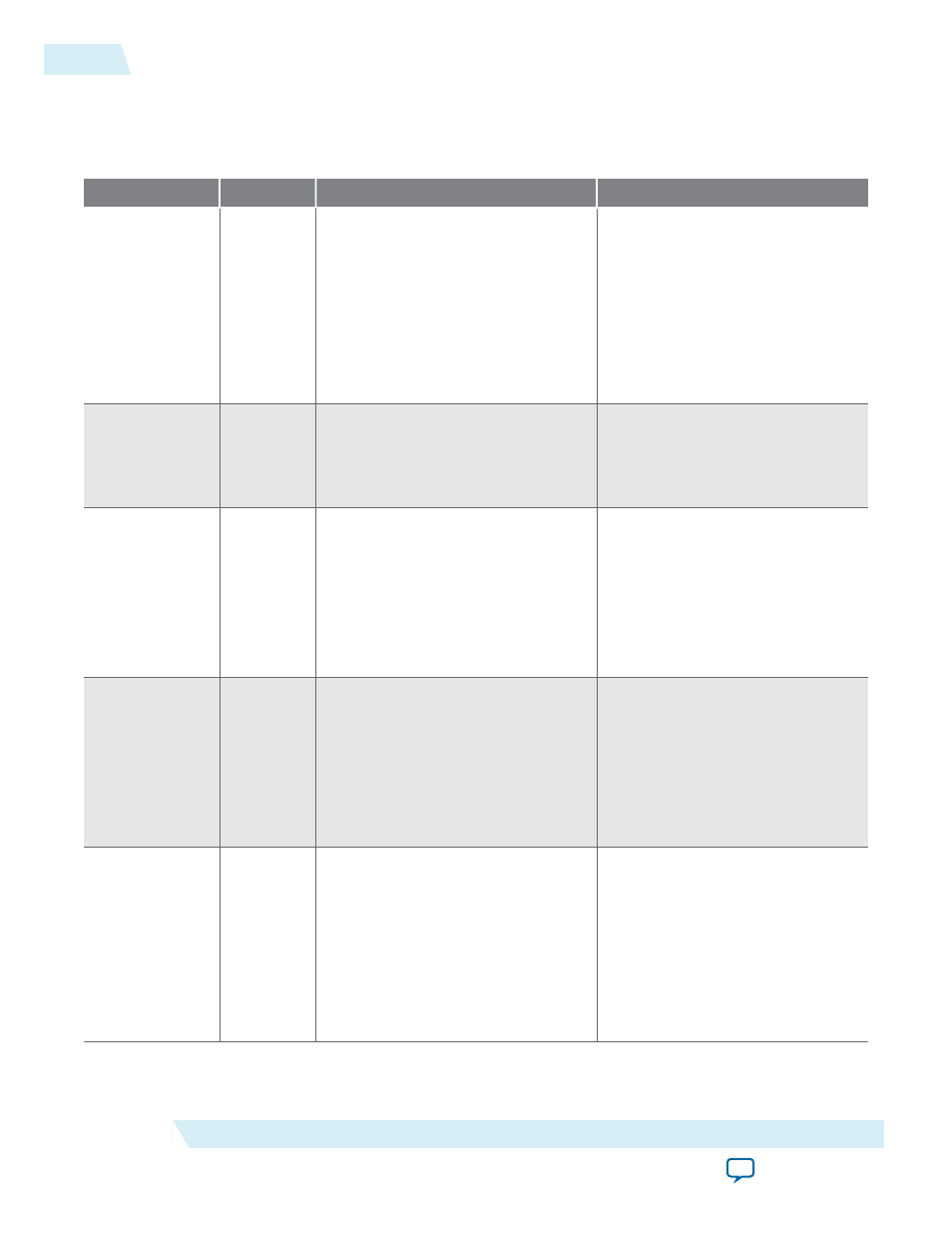

Input Path Signals

Table 20: Input Path Signals

Input path signals are signals that are available when you set the Pin Type parameter to Input or Bidirectional.

Signal Name

Direction

Width

Description

data_to_core

Output

Quarter-rate DDR: 8 x

PIN_WIDTH

Half-rate DDR: 4 x

PIN_WIDTH

Full-rate DDR: 2 x

PIN_WIDTH

Quarter-rate SDR: 4 x

PIN_WIDTH

Half-rate SDR: 2 x

PIN_WIDTH

Full-rate SDR: 1 x

PIN_WIDTH

Valid on

rdata_valid

. Synchro‐

nous to the

core_clk

output from

the IP core.

rdata_en

Input

Quarter-rate: 4

Half-rate: 2

Full-rate: 1

Held high for the number of

expected read words after a read

command. Synchronous to the

core_clk

output from the IP core.

rdata_valid

Output

Quarter-rate: 4

Half-rate: 2

Full-rate: 1

Delayed by

READ_LATENCY

with

margin and aligned to the core

clock rate. For example, in

quarter-rate, the delay will be a

multiple of 4 external clock cycles.

Synchronous to the

core_clk

output from the IP core.

data_in/

data_io

Input/

Bidirectiona

l

•

1 to 48 if data configuration is

Single Ended

•

1 to 24 if data configuration is

Differential

Data input from pin. Synchronous

to the

strobe_in

or

strobe_io

input.

If the pin type is set to Input, the

data_in

ports are used. If the pin

type is set to bidirectional, the

data_io

ports are used.

data_in_n/

data_io_n

Input/

Bidirectiona

l

1 to 24

Negative data input from pin

enabled when data configuration

is set to Differential. Data is

synchronous to the

strobe_in

or

strobe_io

input. If the pin type is

set to Input, the

data_in_n

ports

are used. If the pin type is set to

bidirectional, the

data_io_n

ports are used.

40

Input Path Signals

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide