Altera PHYLite User Manual

Page 59

Manual Migration between ALTDQ_DQS2 and Altera PHYLite for Parallel Interfaces IP Cores

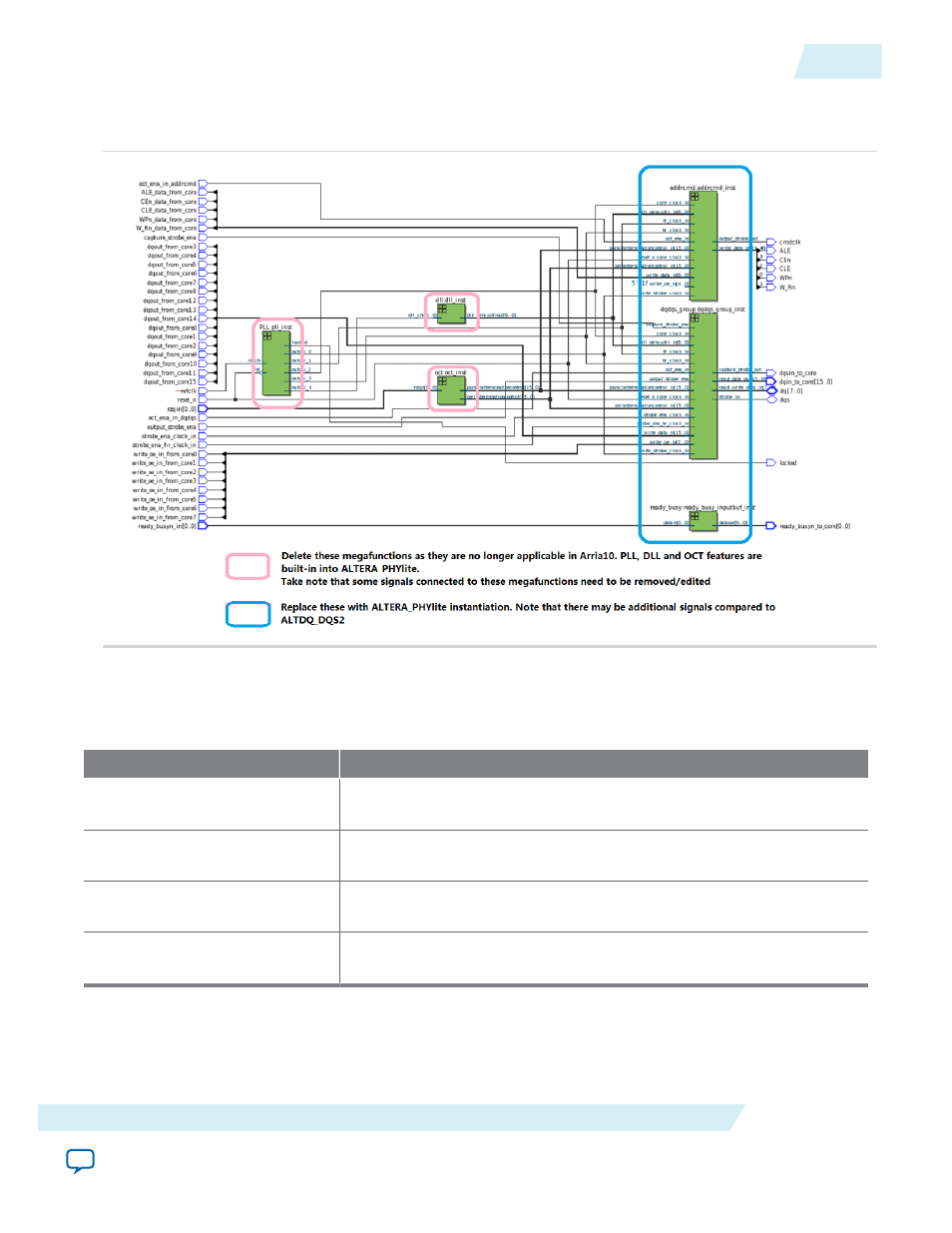

Figure 35: Migration Process Overview for the NAND Flash Simple Design

1. After generating and instantiating the equivalent Altera PHYLite for Parallel Interfaces IP core, delete

the ALTERA_PLL, ALTDLL and ALTOCT IP cores.

2. Remove the connections between the ALTERA_PLL, ALTDLL, ALTOCT IP cores and the rest of the

design in the RTL.

Signal

Description

oct_ena_in

Remove this connection. The OCT is built-in in Altera PHYLite for

Parallel Interfaces IP core.

strobe_ena_clock_in

Remove this connection. The DQS enable is built-in in Altera PHYLite

for Parallel Interfaces IP core.

strobe_ena_hr_clock_in

Remove this connection. The DQS enable is built-in in Altera PHYLite

for Parallel Interfaces IP core.

capture_strobe_out

Remove this connection. This signal is not available for Arria 10

devices.

3. Connect the Altera PHYLite for Parallel Interfaces IP core signals appropriately to the design in the

RTL. The

core_clock

and

rdata_valid

signals are examples of additional signal from the

ALTERA_PHYlite which will be feeding the core logic. The following table lists information about

connecting similar or new signals.

ug_altera_phylite

2015.01.16

Manual Migration between ALTDQ_DQS2 and Altera PHYLite for Parallel Interfaces

IP Cores

59

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation