Altera PHYLite User Manual

Page 32

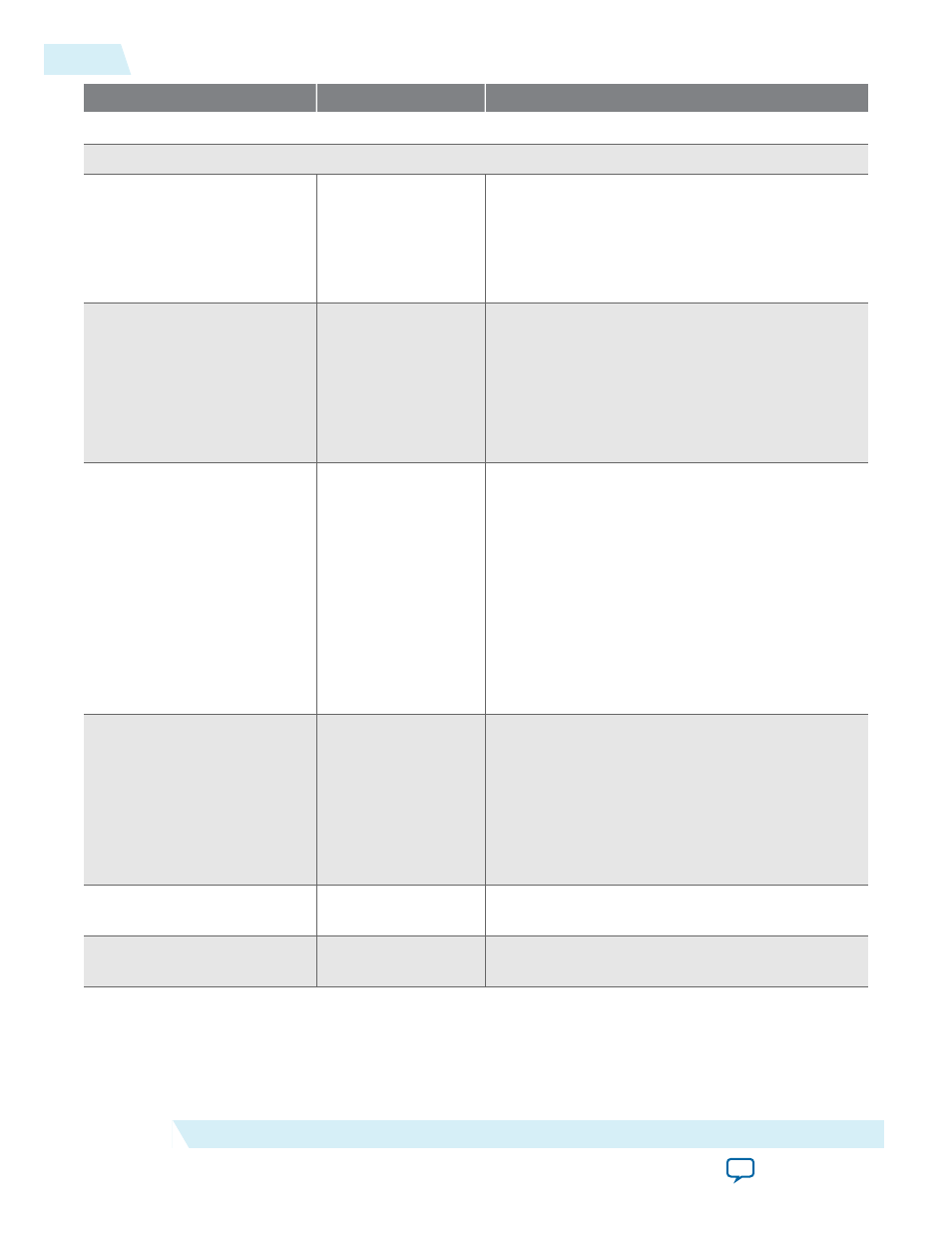

GUI Name

Values

Description

General Tab- these parameters are set on a per interface basis

Clocks

Memory clock frequency

100 MHz - 1333.333

MHz

External memory clock frequency. The value is set

to 533 MHz by default.

Note: To achieve timing closure at 800 MHz

and above, use dynamic reconfigura‐

tion to calibrate the interface.

Use recommended PLL

reference clock frequency

—

If you want to calculate the PLL reference clock

frequency automatically for best performance,

then turn on this option.

If you want to specify your own PLL reference

clock frequency, then turn off this option.

This option is enabled by default.

PLL reference clock

frequency

Dependent on desired

memory clock

frequency

PLL reference clock frequency. You must feed a

clock of this frequency to the PLL reference clock

input of the memory interface. The default value is

dependent on recommended clock frequency and

user clock rate.

Note: There is no minimum range, but the

maximum output frequency is 1600

MHz limited by the clock network. The

minimum range for the

ref_clk

signal

is 10 MHz but the maximum is

dependent on the speed grade.

Clock rate of user logic

Full, Half, Quarter

Determines the clock frequency of user logic in

relation to the memory clock frequency. For

example, if the memory clock sent from the FPGA

to the memory device is toggling at 800 MHz, a

"Quarter rate" interface means that the user logic

in the FPGA runs at 200 MHz.

The value is set to Quarter by default.

Specify additional output

clocks based on existing PLL

—

Exposes additional output clocks from the existing

PLL.

Number of additional clocks

0 to 4

Specifies the number of additional clocks to be

exposed.

32

Parameter Settings

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide