Altera PHYLite User Manual

Page 50

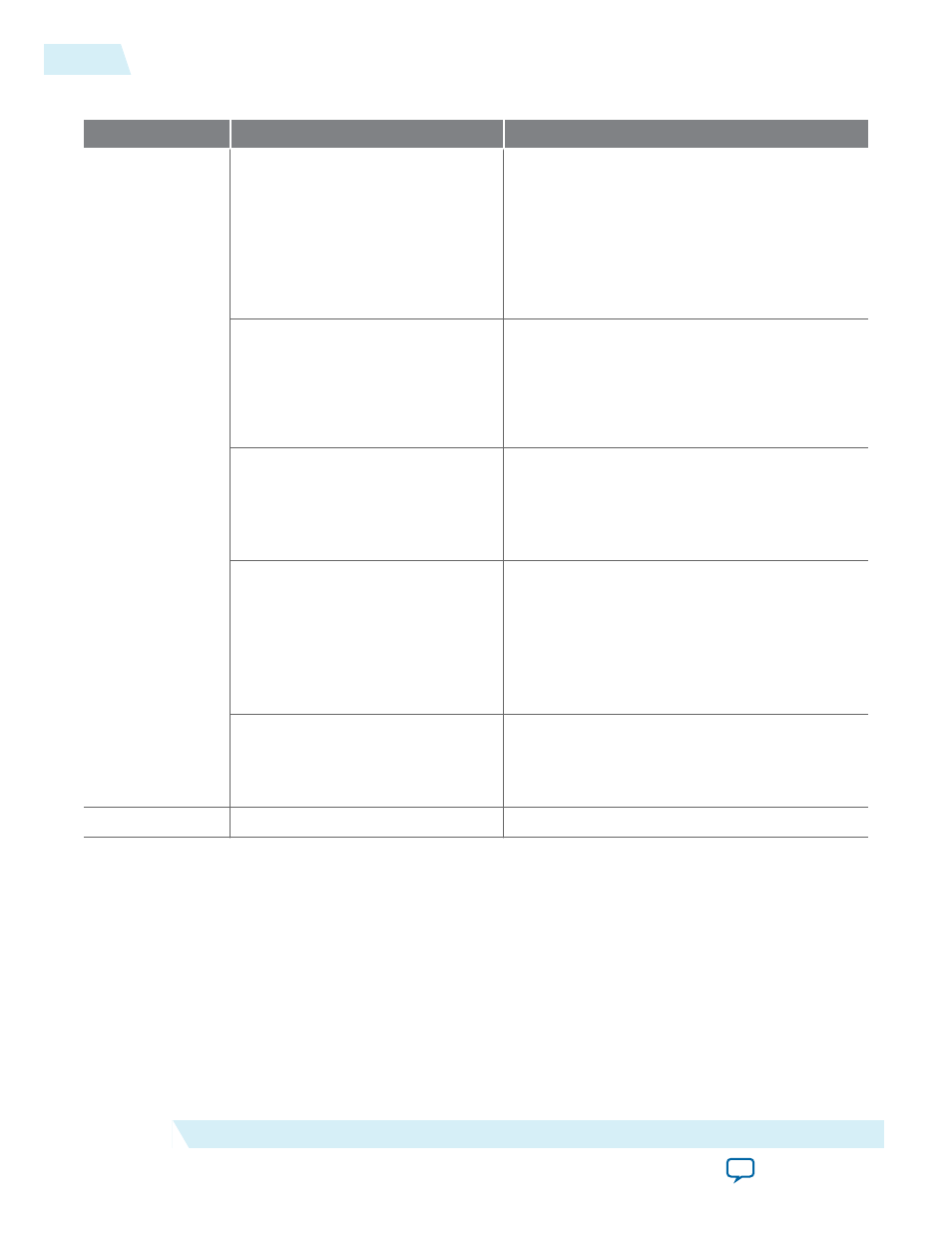

Table 25: ALTDQ_DQS2 IP Core Specific Parameters

Section

Parameter

Description

General Settings

Extra output-only pins

This option is commonly used as datamask pins

in the ALTDQ_DQS2 IP core. In the Altera

PHYLite for Parallel Interfaces IP core, you may

implement this as part of the data group.

Note: An I/O bank comprises of 48 I/O

pins (up to 48 data I/Os as well as the

strobe capture logic).

Use DLL Offset Control

You cannot access the DLL because the DLL is

an internal block in Arria 10 devices.

Note: This feature is only for testing

purposes in the ALTDQ_DQS2 IP

core.

Enable hard FIFOs

In Arria 10 devices, the FIFOs are built-in and

is always enabled. But you can decide on the

full/half/quarter rate conversion to achieve the

equivalent data width and rate with the

ALTDQ_DQS2 IP core.

Enable dual write clocks

Enabled the use of separate output clocks for

data and strobe in the ALTDQ_DQS2 IP core.

Equivalent implementation is available in the

Altera PHYLite for Parallel Interfaces IP core.

You can control the phase shift with the Output

Strobe Phase parameter in the Altera PHYLite

for Parallel Interfaces IP core.

Use capture clock to clock the read

side of the Hard FIFO (For Arria V

and Cyclone V devices only)

This feature is not supported in the Altera

PHYLite for Parallel Interfaces IP core. This

parameter is only available for Arria V and

Cyclone V devices.

Output Path

Use output phase alignment blocks

Arria 10 devices have different architecture.

50

Parameters for ALTDQ_DQS2 IP Core Only

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide