Document revision history – Altera PHYLite User Manual

Page 60

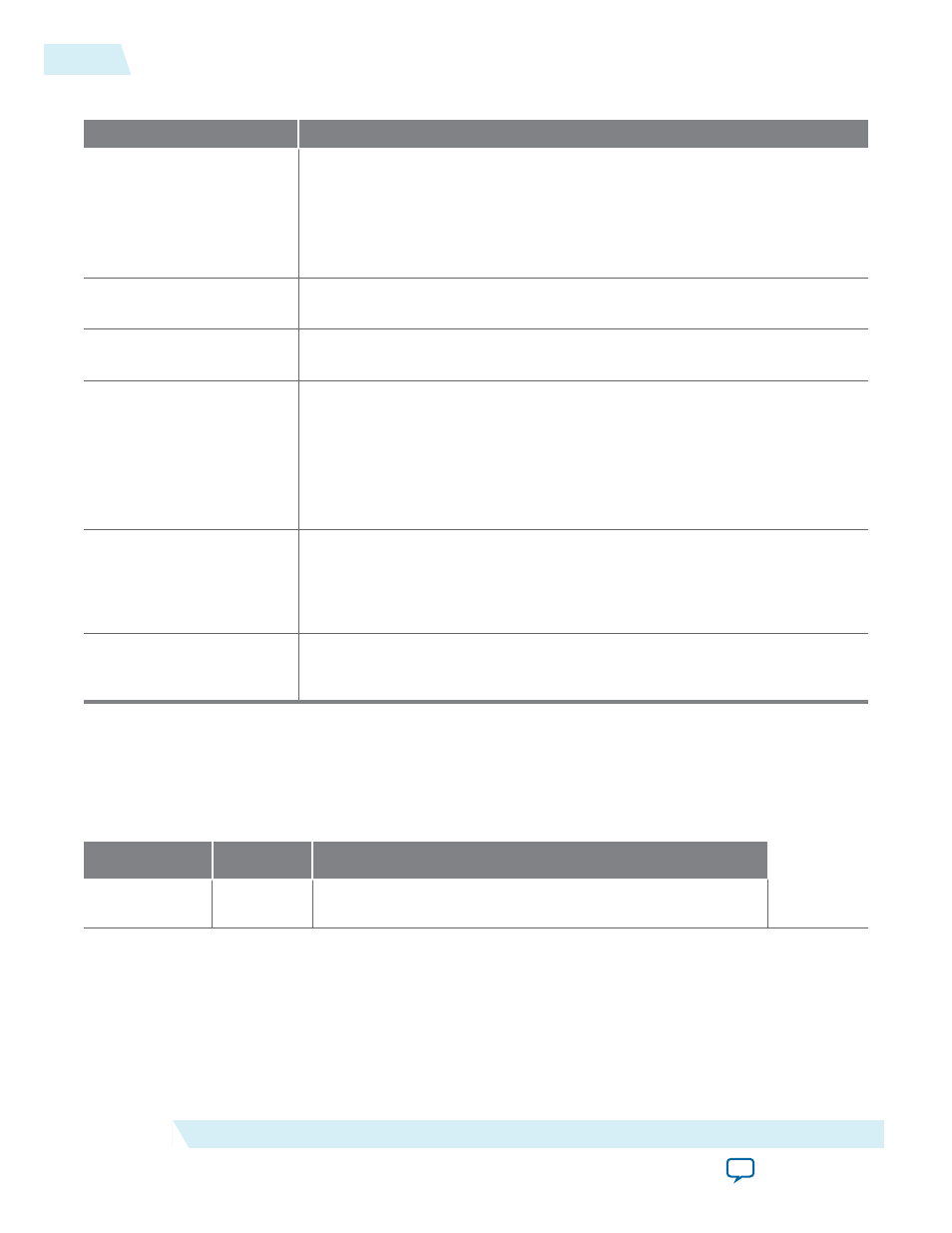

Table 27: Connecting Similar or New Signals

Signal

Description

rdata_en

In the Altera PHYLite for Parallel Interfaces IP core, this signal is similar but

not exactly the same as the

capture_strobe_ena

in the ALTDQ_DQS2 IP

core.

Connect this signal to the core. This signal must be held high for the number

of expected read words after a read command.

rzqin

You must manually create this signal in the Altera PHYLite for Parallel

Interfaces IP core using the QSF assignments in Arria 10 devices.

core_clk_out

A new signal for the Altera PHYLite for Parallel Interfaces IP core. This signal

was created because the PLL is built-in for Arria 10 devices.

rdata_valid

This signal is a delayed

rdata_en

signal by READ_LATENCY + 6. Because

the

data_to_core

signal is valid on

rdata_valid

, feed the

rdata_valid

signal to the core appropriately to know when the correct

data_to_core

is

expected.

Always matches the

rdata_en

on page 8

section.

strobe_out_in

Use this signal to send customized strobe data pattern.

This signal is synchronous to the

core_clk

output from the IP core.

This signal is controlled from the core.

strobe_out_en

This signal enables the output strobe.

This signal is controlled from the core.

4. Run Analysis and Elaboration to confirm that the manual IP migration is successful.

Document Revision History

Table 28: Document Revision History

Date

Version

Changes

January 2015 2015.01.28

Updated related information link to Functional Description for

External Memory Interfaces in Arria 10 Devices.

60

Document Revision History

ug_altera_phylite

2015.01.16

Altera Corporation

Altera PHYLite for Parallel Interfaces IP Core User Guide