Avalon configuration bus interface signals – Altera PHYLite User Manual

Page 41

Signal Name

Direction

Width

Description

strobe_in/

strobe_io

Input/

Bidirectiona

l

1

Positive strobe from pin. If the pin

type is set to Input, the

strobe_in

signal is used. If the pin type is set

to Bidirectional, the

strobe_io

signal is used.

strobe_in_n/

strobe_io_n

Input/

Bidirectiona

l

1

Negative strobe from pin. This is

used if the Strobe Configuration

parameter is set to Differential or

Complementary. If the pin type is

set to Input, the

strobe_in_n

signal is used. If the pin type is set

to Bidirectional, the

strobe_io_n

signal is used.

Avalon Configuration Bus Interface Signals

The Altera PHYLite for Parallel Interfaces IP core exposes the Avalon-MM slave and Avalon-MM master

interfaces when you perform dynamic reconfiguration. Connect the Avalon-MM slave to either a master

in the core or the master interface of either an Altera PHYLite for Parallel Interfaces IP core or the Arria

10 External Memory Interfaces IP core to be placed in the same column. You can only connect the master

interface to the slave interface of an Altera PHYLite for Parallel Interfaces IP core or an Arria 10 External

Memory Interfaces IP core to be placed in the same column.

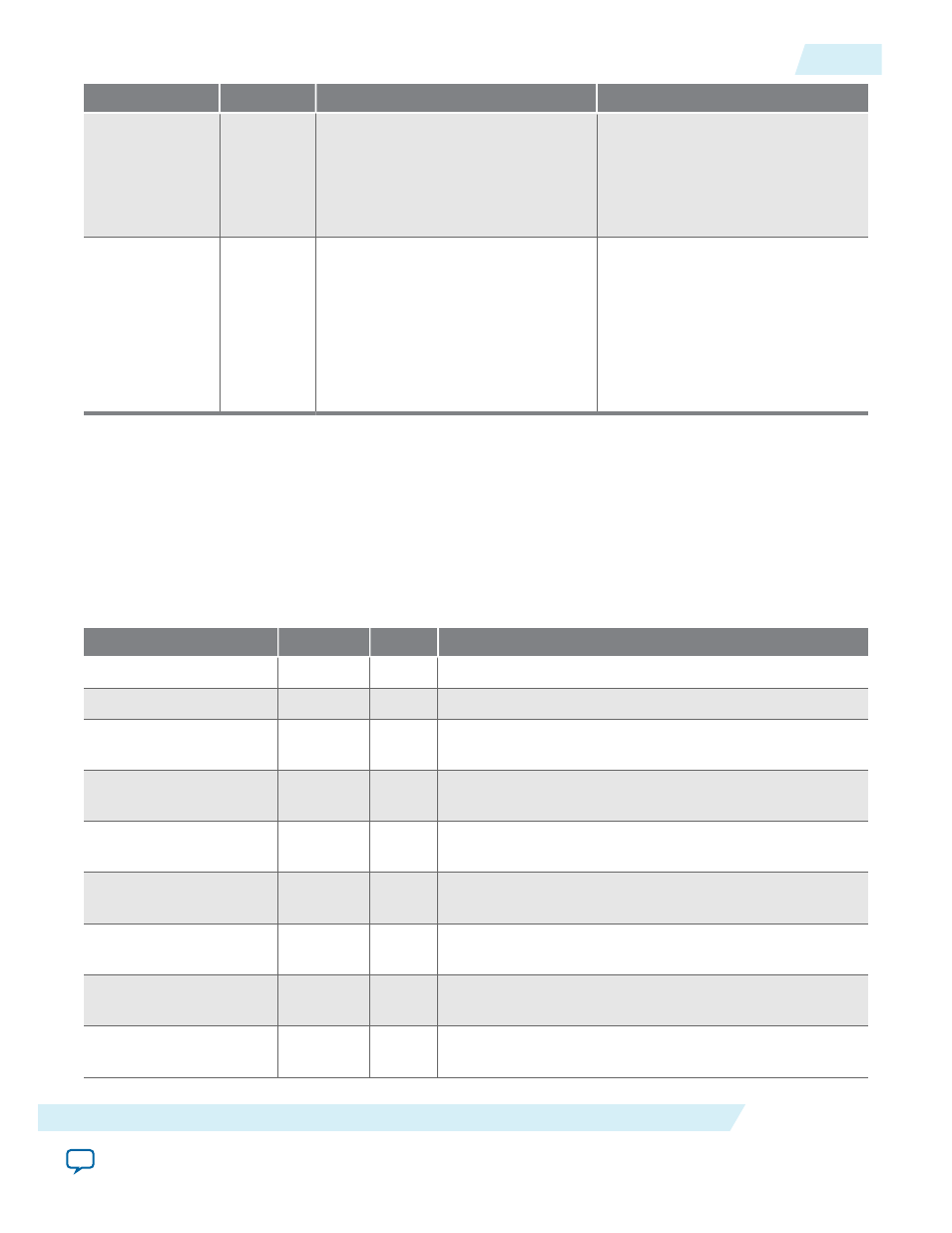

Table 21: Avalon-MM Master Interface Signals

Signal Name

Direction

Width

Description

avl_clk

Input

1

Avalon interface clock.

avl_reset_n

Input

1

Reset input synchronous to

avl_clk

.

avl_read

Input

1

Read request from

io_aux

. This signal is synchronous to

the

avl_clk

input.

avl_write

Input

1

Write request from

io_aux

. This signal is synchronous to

the

avl_clk

input.

avl_byteenable

Input

4

Controls which bytes should be written on

avl_

writedata

.

avl_writedata

Input

32

Write data from io_aux. This signal is synchronous to the

avl_clk input.

avl_address

Input

28

Address from

io_aux

. This signal is synchronous to the

avl_clk

input.

avl_readdata

Output

32

Read data to

io_aux

. This signal is synchronous to the

avl_clk

input.

avl_writedata

Input

32

Write data from

io_aux

. This signal is synchronous to

the

avl_clk

input.

ug_altera_phylite

2015.01.16

Avalon Configuration Bus Interface Signals

41

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation