Altera PHYLite User Manual

Page 33

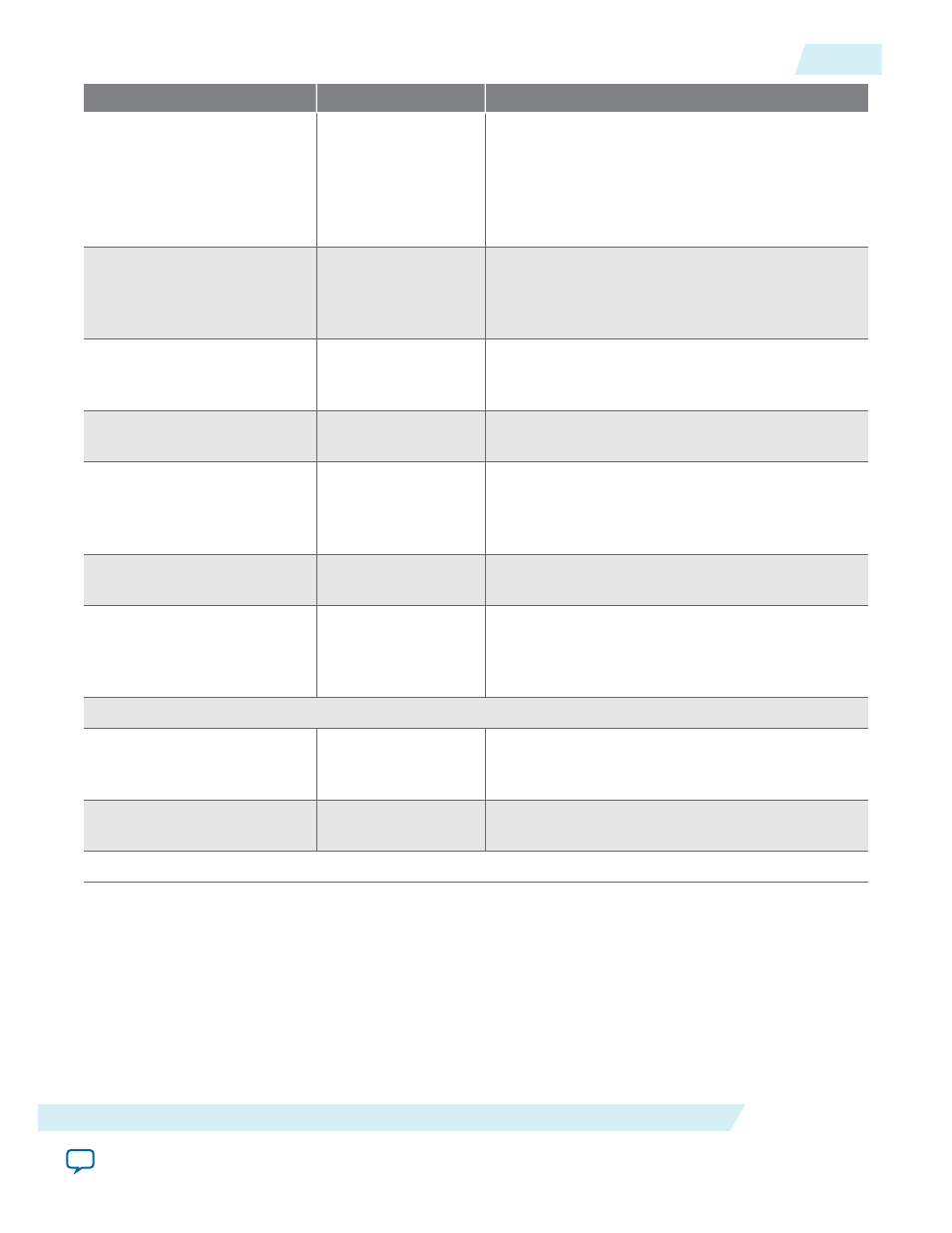

GUI Name

Values

Description

Desired Frequency

—

Specifies the output clock frequency of the

corresponding output clock port,

outclk[]

, in

MHz. The default value is 100.0 MHz. The

minimum and maximum values depend on the

device used. The PLL only reads the numerals in

the first six decimal places.

Actual Frequency

—

Allows you to select the actual output clock

frequency from a list of achievable frequencies.

The default value is the closest achievable

frequency to the desired frequency.

Phase Shift units

ps or degrees

Specifies the phase shift unit for the corresponding

output clock port,

outclk[]

, in picoseconds (ps)

or degrees.

Phase Shift

—

Specifies the requested value for the phase shift.

The default value is 0 ps.

Actual Phase Shift

—

Allows you to select the actual phase shift from a

list of achievable phase shift values. The default

value is the closest achievable phase shift to the

desired phase shift.

Desired Duty Cycle

0.0–100.0

Specifies the requested value for the duty cycle.

The default value is 50.0%

Actual Duty Cycle

—

Allows you to select the actual duty cycle from a

list of achievable duty cycle values. The default

value is the closest achievable duty cycle to the

desired duty cycle.

Dynamic Reconfiguration

Use dynamic reconfigura‐

tion

—

Exposes an Avalon-MM interface, allowing you to

control the configuration of the Altera PHYLite

for Parallel Interfaces IP core settings.

Interface ID

0

The ID used to identify this interface in the

column over the Avalon-MM bus.

I/O Settings

ug_altera_phylite

2015.01.16

Parameter Settings

33

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation