Implementation using the altdq_dqs2 ip core – Altera PHYLite User Manual

Page 53

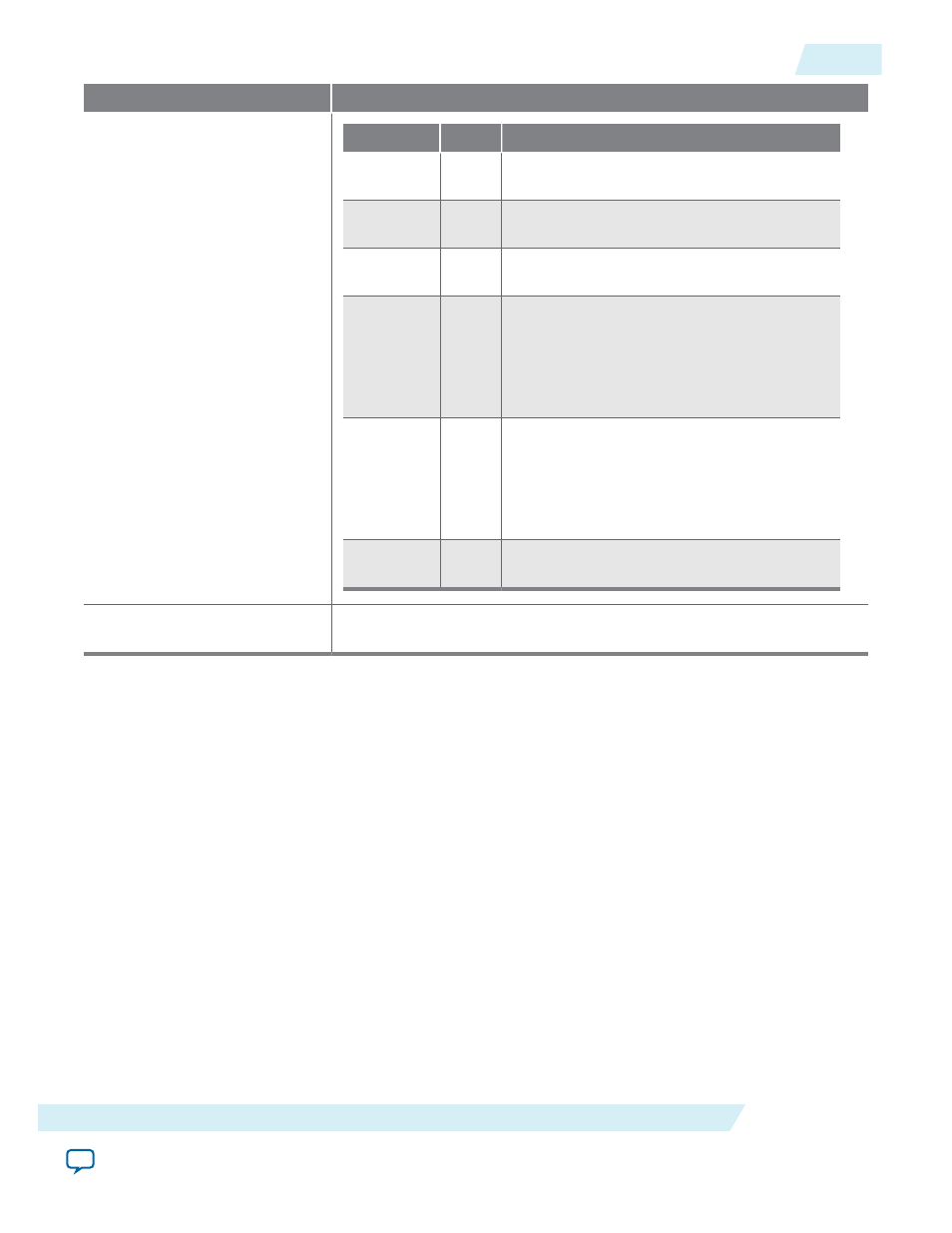

Synchronous Signals

Description

CMD/ADDR signals (output

from FPGA, input to memory)

Signal

Type

Description

ALE

Input Address latch enable. Loads an address

from DQx into the address register.

CE#

Input Chip enable. Enables or disables one or

more die (LUNs) in a target.

CLE

Input Command latch enable. Loads a command

from DQx into the command register.

W/R#

Input Read enable and write/read enable. RE#

transfers serial data from the NAND Flash

to the host system when the asynchronous

interface is active. When the synchronous

interface is active, WR# controls the

direction of DQx and DQS.

CLK

Input Write enable and clock. WE# transfers

commands, addresses, and serial data from

the host system to the NAND Flash when

the asynchronous interface is active. When

the synchronous interface is active, CLK

latches command and address cycles.

WP#

Input Write protect. Enables and disables array

PROGRAM and ERASE operations.

R/B# (output from memory,

input to the FPGA.)

Ready/Busy. This signal is an open-drain, active-low output that requires

an external pull-up resistor. This signal indicates target array activity.

Implementation Using the ALTDQ_DQS2 IP Core

The following lists the possible implementations when you target Arria V, Cyclone V, and Stratix V

devices:

• Instantiates two ALTDQ_DQS2 IP cores.

• Bidirectional type for DQ and DQS (

)

)

• Instantiates a ALTIOBUF (input) for the

ready

signal

• Connects the ALTERA_PLL, ALTDLL, and ALTOCT IP cores to complete the PHY-only design.

ug_altera_phylite

2015.01.16

Implementation Using the ALTDQ_DQS2 IP Core

53

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation