Placement restrictions, Group pin placement – Altera PHYLite User Manual

Page 15

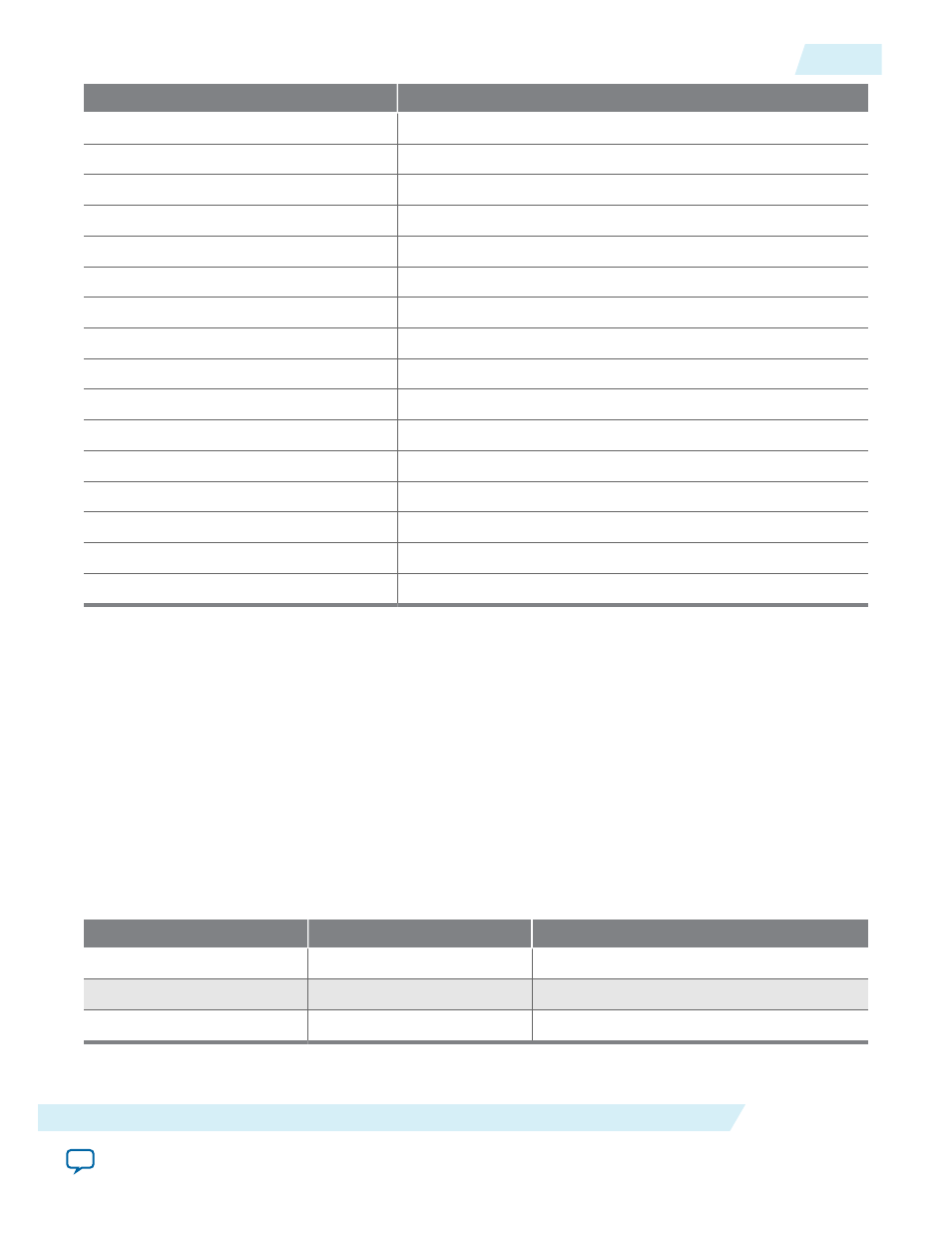

avl_writedata[5:0]

% of VCCN

100100

83.04%

100101

83.68%

100110

84.32%

100111

84.96%

101000

85.60%

101001

86.24%

101010

86.88%

101011

87.52%

101100

88.16%

101101

88.80%

101110

89.44%

101111

90.08%

110000

90.72%

110001

91.36%

110010

92.00%

110011 -> 111111

Reserved

Related Information

on page 16

For more information on the Avalon bus usage

Placement Restrictions

Group Pin Placement

Place each group in the interface into a set of lanes in the same bank, the number of which depends on the

number of pins used by the group. All groups in an interface must be placed across a contiguous set of

banks.

Table 8: Group Pin Placement

Number of Pins in Group

Valid DQS Group in a Bank

Valid Indices in a Bank

1-12

DQS for X8/X9

{0-11}/{12-23}/{24-35}/{36-47}

13-24

DQS for X16/X18

{0-23}/{24-47}

24-48

DQS for X32/X36

{0-47}

ug_altera_phylite

2015.01.16

Placement Restrictions

15

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation