Tx_ctrl register, Tx_ctrl register -12 – Altera CPRI v6.0 MegaCore Function User Manual

Page 101

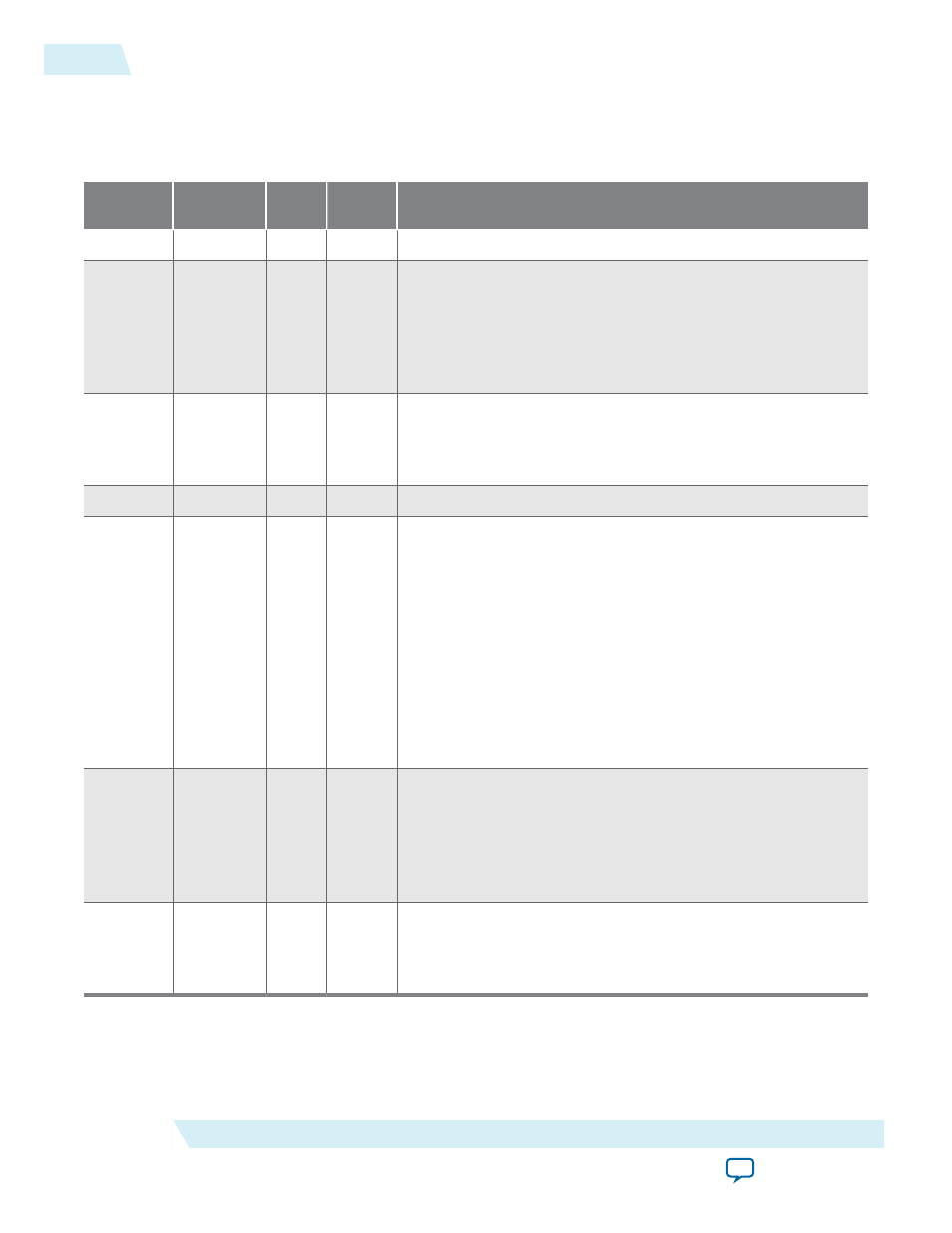

Table 5-15: CPRI v6.0 IP Core CTRL_INDEX Register at Offset 0x30

Frequency differences between the control and status interface clock

cpu_clk

and the main CPRI v6.0 IP core

clock

cpri_clkout

might cause non-zero read latency and more than one clock cycle of write latency when

accessing this register.

Bits

Field Name

Type

Value on

Reset

Description

31:27

Reserved

UR0

5'b0

26:24

rx_ctrl_

seq

RW

3'b0

Sequence number for CPRI control word 32-bit section

monitoring. The value in this field determines the 32-bit

section of the control receive table entry that appears in the

RX_

CTRL

register. The value indicates whether this is the first,

second, third, fourth, or fifth (for RTVS) 32-bit section in the

control word.

23:16

rx_ctrl_x

RW

8'b0

Index for CPRI control word monitoring (X value in frame

location #Z.X.Y). The value in this field determines the control

receive table entry of which a 32-bit section appears in the

RX_

CTRL

register.

15:12

Reserved

UR0

4'b0

11

tx_ctrl_

insert

RW

1'b0

Control word 32-bit section transmit enable. This value is

stored in the control transmit table with its associated entry.

When you change the value of the

tx_ctrl_seq

field or the

tx_

ctrl_x

field, the stored

tx_ctrl_insert

bit associated with

the indexed entry appears in the

tx_ctrl_insert

field.

At the time the CPRI v6.0 IP core can insert a control transmit

table entry in the associated position in the outgoing

hyperframe on the CPRI link, if the

tx_ctrl_insert

bit

associated with that entry has the value of 1, and the

tx_ctrl_

insert_en

bit of the

L1_CONFIG

register is asserted, the IP core

inserts the table entry in the hyperframe.

10:8

RW

3'b0

Sequence number for CPRI control word 32-bit section

insertion. The value in this field determines the 32-bit section

of the control transmit table entry that appears in the

TX_CTRL

register. The value indicates whether this is the first, second,

third, fourth, or fifth (for RTVS) 32-bit section in the control

word.

7:0

RW

8'b0

Index for CPRI control word insertion (X value in frame

location #Z.X.Y). The value in this field determines the control

transmit table entry of which a 32-bit section appears in the

TX_

CTRL

register.

TX_CTRL Register

5-12

TX_CTRL Register

UG-01156

2015.02.16

Altera Corporation

CPRI v6.0 IP Core Registers