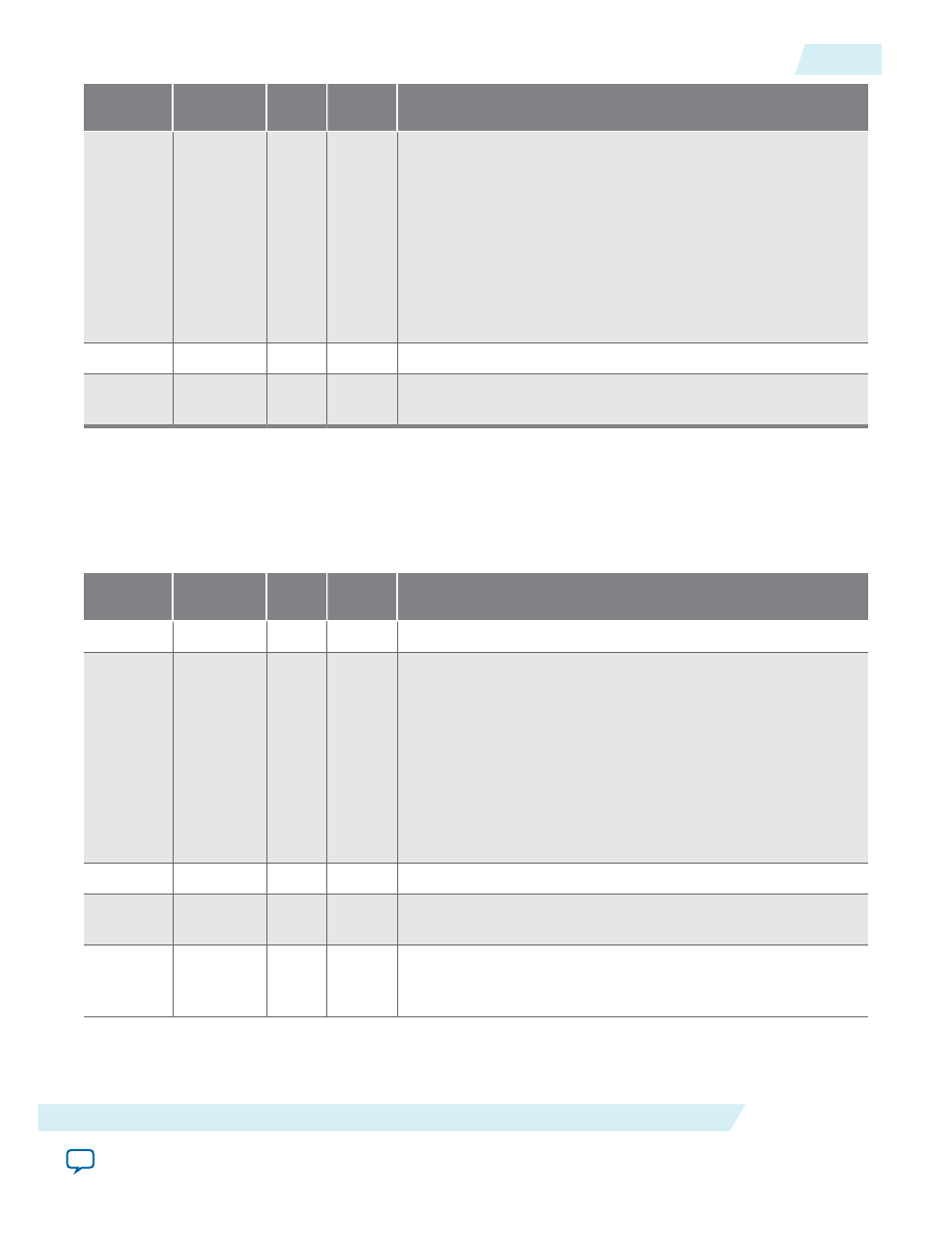

Rx_delay register, Rx_delay register -17 – Altera CPRI v6.0 MegaCore Function User Manual

Page 106

Bits

Field Name

Type

Value on

Reset

Description

8

tx_buf_

resync

RW

1'b0

Force transmit buffer pointer resynchronization. You can use

this register field to resynchronize if, for example, the buffer fill

level becomes too high due to due to environmental impacts on

the device, such as temperature. Resynchronizing might lead to

data loss or corruption.

Do not use this register field to resynchronize after a dynamic

CPRI line bit rate change. After a dynamic CPRI line bit rate

change the IP core forces resynchronization internally without

referring to this register.

7:4

Reserved

UR0

4'b0

3:0

tx_buf_

delay

RO

4'b0

Current transmit buffer fill level.

RX_DELAY Register

Table 5-22: CPRI v6.0 IP Core RX_DELAY Register at Offset 0x4C

Bits

Field Name

Type

Value on

Reset

Description

31:25

Reserved

UR0

7'b0

24

rx_buf_

resync

RW

1'b0

Force receive buffer pointer resynchronization. You can use

this register field to resynchronize if, for example, the buffer fill

level becomes too high due to due to environmental impacts on

the device, such as temperature. Resynchronizing might lead to

data loss or corruption.

Do not use this register field to resynchronize after a dynamic

CPRI line bit rate change. After a dynamic CPRI line bit rate

change the IP core forces resynchronization internally without

referring to this register.

23:17

Reserved

UR0

7'b0

16

rx_byte_

delay

RO

1'b0

Current byte-alignment delay. This field is relevant for the Rx

path delay calculation.

15:

RX_

BUF_

DEPTH

Reserved

UR0

0

UG-01156

2015.02.16

RX_DELAY Register

5-17

CPRI v6.0 IP Core Registers

Altera Corporation