Altera CPRI v6.0 MegaCore Function User Manual

Page 20

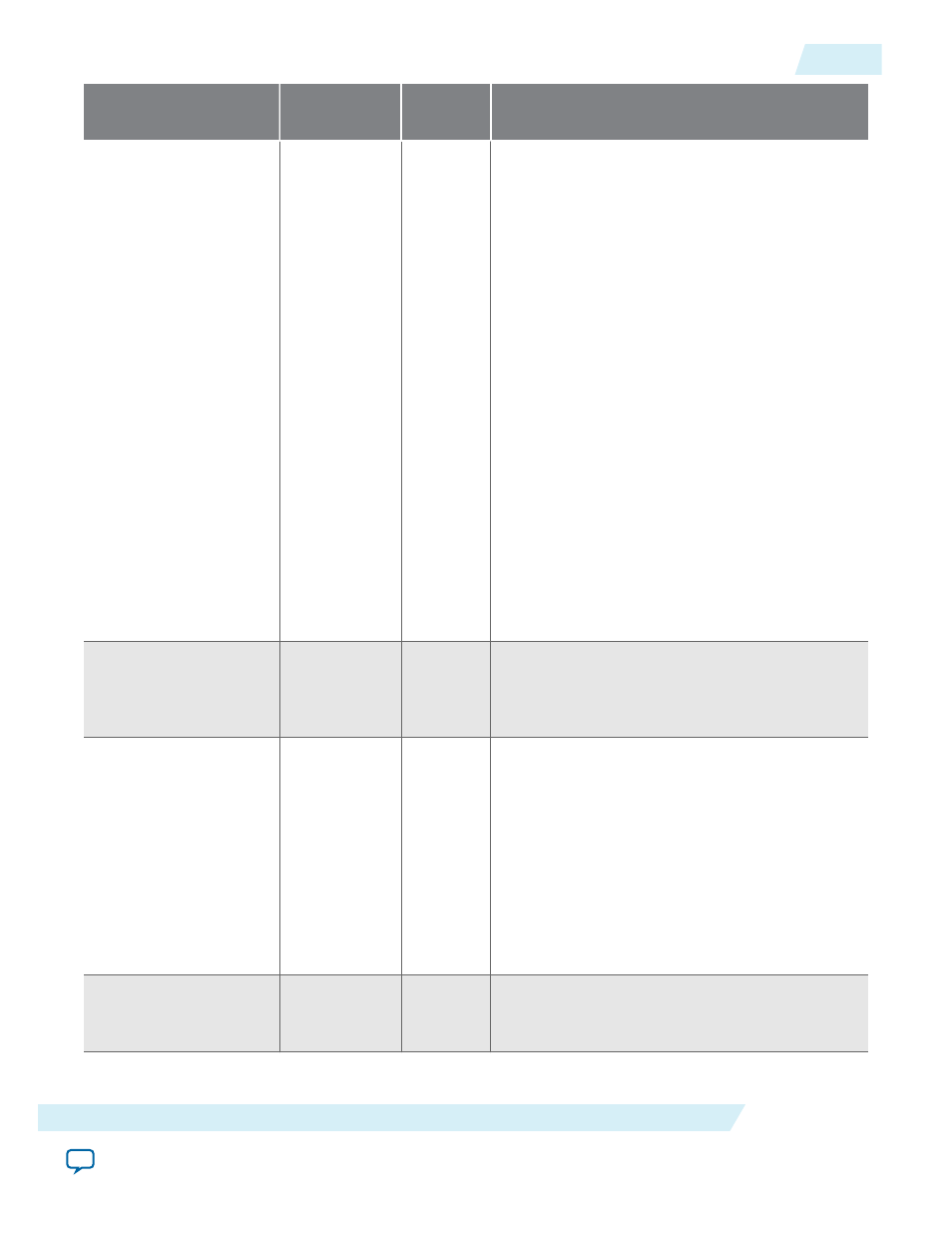

Parameter

Range

Default

Setting

Parameter Description

Auxiliary latency

cycle(s)

0 to 9

0

Specifies the additional write latency on the AUX

TX interface and other direct TX interfaces to the

CPRI v6.0 IP core. The write latency is the

number of

cpri_clkout

cycles from when the

aux_tx_seq

output signal has the value of 0 to

when user logic writes data to the AUX TX

interface. For other direct interfaces, the IP core

notifies user logic when it is ready for input and

the user does not need to monitor the

aux_tx_

seq

signal.

When Auxiliary latency cycle(s) has the value of

zero, the write latency on the direct TX interfaces

is one

cpri_clkout

cycle. When Auxiliary

latency cycle(s) has the value of N, the write

latency is (1+N)

cpri_clkout

cycles.

Set this parameter to a value that provides user

logic with sufficient advance notice of the

position in the CPRI frame. The processing time

that user logic requires after determining the

current position in the CPRI frame is implemen‐

tation specific.

This parameter is available if you turn on at least

one direct interface in your CPRI v6.0 IP core

variation.

Enable auxiliary

interface

• On

• Off

Off

Turn on this parameter to include the AUX

interface in your CPRI v6.0 IP core. The AUX

interface provides full access to the raw CPRI

frame.

Enable all control

word access

• On

• Off

Off

Turn on this parameter to enable access to all

control words in a hyperframe using the CPRI

v6.0

CTRL_INDEX

,

TX_CTRL

, and

RX_CTRL

registers.

Use this option with caution. During transmis‐

sion, this feature has higher priority than the MII,

the HDLC serial interface, the L1 control and

status interface, and the generation of special

symbols (K28.5, D16.2, /S/, /T/) , and can

overwrite standard control words in the

hyperframe.

Enable direct IQ

mapping interface

• On

• Off

Off

Turn on this parameter to include a dedicated

interface to access the raw I/Q data bytes in the

CPRI frame.

UG-01156

2014.08.18

CPRI v6.0 IP Core Parameters

2-9

Getting Started with the CPRI v6.0 IP Core

Altera Corporation