Altera CPRI v6.0 MegaCore Function User Manual

Page 43

Advertising

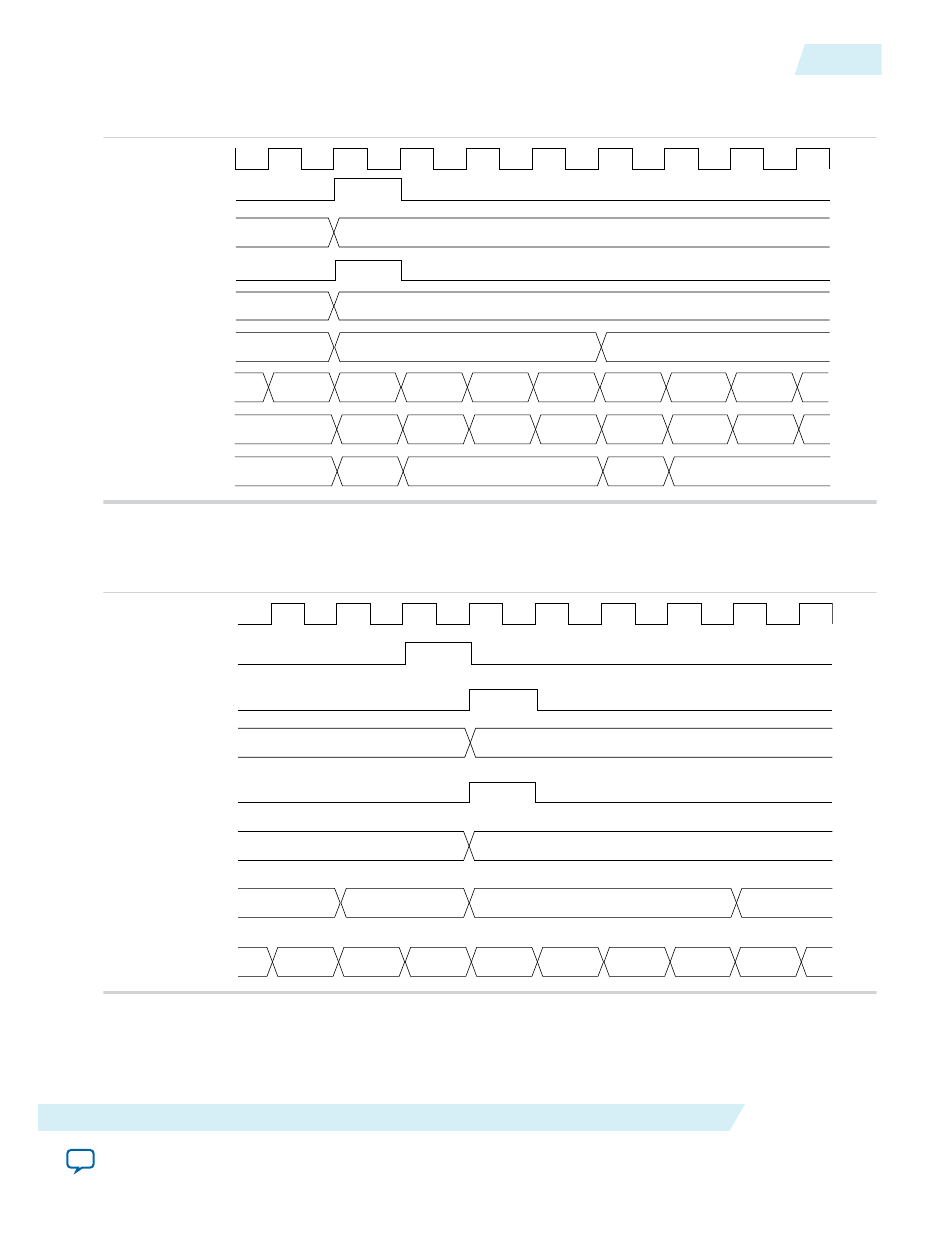

Figure 3-5: AUX RX Interface Timing Diagram

AUX RX interface behavior in a CPRI v6.0 IP core running at 0.6144 Gbps.

4095

0

0

3

255

1

149

0

2

0

1

2

3

0

1

2

X

Data #1

Data #2

Data #3

Data #4

Data #5

cpri_clkout

aux_rx_rfp

aux_rx_bfn

aux_rx_hfp

aux_rx_z

aux_rx_x

aux_rx_seq

aux_rx_data

aux_rx_ctrl[3:0]

Data #6

0000

1000

0000

Data #7

X

1000

Figure 3-6: CPRI REC Master Response to aux_tx_sync_rfp Resynchronization Pulse

Asserting

aux_tx_sync_rfp

resets the hyperframe and basic frame numbers in an REC master CPRI v6.0

IP core. Shown for a CPRI v6.0 IP core running at 0.6144 Gbps.

21

22

216

3

215

1

98

0

2

0

1

0

1

2

3

0

cpri_clkout

aux_tx_rfp

aux_tx_bfn

aux_tx_hfp

aux_tx_hfn

aux_tx_x

aux_tx_seq

aux_tx_sync_rfp

0

UG-01156

2014.08.18

AUX Interface Signals

3-13

Functional Description

Altera Corporation

Advertising