Altera CPRI v6.0 MegaCore Function User Manual

Page 42

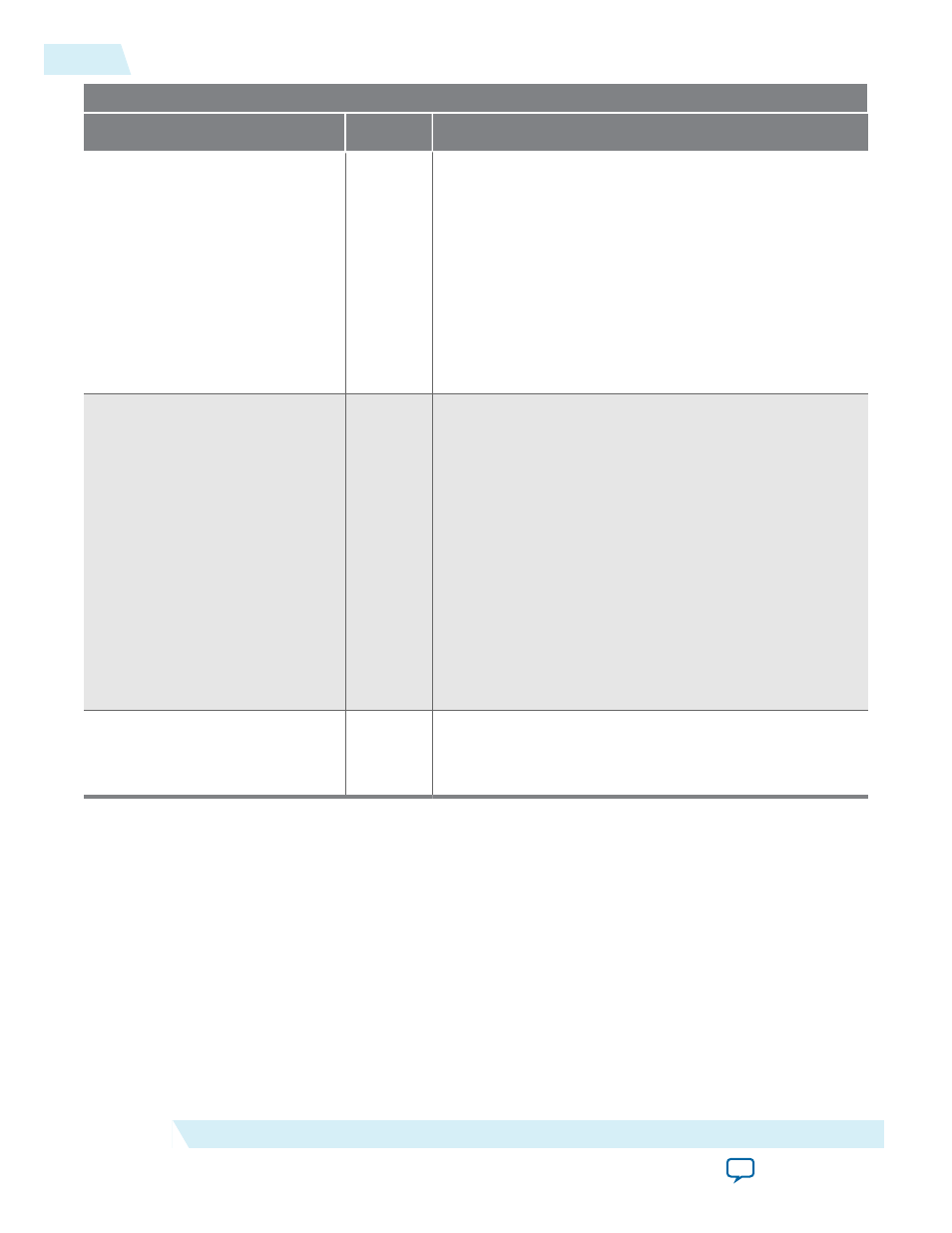

AUX TX Interface Data Signals

Signal Name

Direction

Description

aux_tx_data[31:0]

Input

Data the IP core receives on the AUX TX interface. The

data is aligned with

aux_tx_seq

with a write delay of one

cpri_clkout

cycle plus the number of additional

cpri_

clkout

cycles you specify as the value of the Auxiliary

latency cycle(s) parameter.

User logic is responsible to ensure that the write data in

aux_tx_data

is aligned with the write latency value of the

Auxiliary latency cycle(s) parameter.

Data is received in 32-bit words. For correct transmission

in the CPRI frame, you must send byte [31:24] first and

byte [7:0] last.

aux_tx_mask[31:0]

Input

Bit mask for insertion of data from

aux_tx_data

in the

target CPRI frame.

This signal aligns with

aux_tx_data

and therefore, aligns

with

aux_tx_seq

with a delay of one

cpri_clkout

cycle

plus the number of additional

cpri_clkout

cycles you

specify as the value of the Auxiliary latency cycle(s)

parameter.

Assertion of a bit in this mask overrides insertion of data

to the corresponding bit in the target CPRI frame from

any other source. Therefore, you must deassert the mask

bits during K28.5 character insertion in the outgoing

CPRI frame, which occurs when Z=X=0. If you do not

deassert the mask bits during K28.5 character insertion in

the outgoing CPRI frame, the

aux_tx_err

output signal is

asserted in the following

cpri_clkout

cycle.

aux_tx_ctrl[3:0]

Output

Control slots indicator. Each asserted bit indicates that the

corresponding byte position, as indicated by

aux_tx_seq

,

should hold a CPRI control word in the target CPRI

frame.

3-12

AUX Interface Signals

UG-01156

2014.08.18

Altera Corporation

Functional Description