Altera CPRI v6.0 MegaCore Function User Manual

Page 109

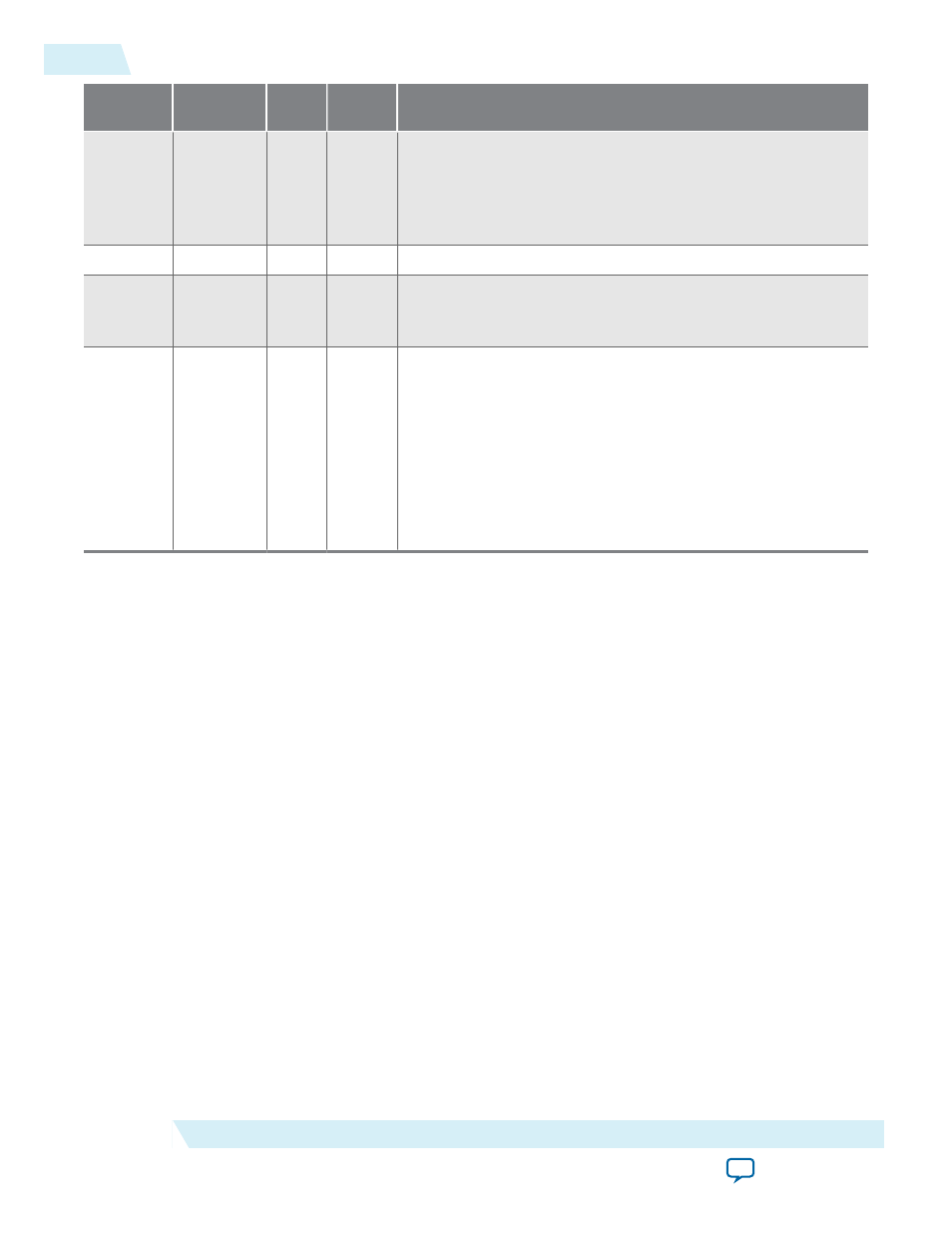

Bits

Field Name

Type

Value on

Reset

Description

20:16

rx_

bitslip_

out

RO

5'b0

Number of bits of delay (bitslip) detected at the receiver word-

aligner. Value can change at frame synchronization, when the

transceiver is resetting. Any K28.5 symbol position change that

occurs when word alignment is activated changes the bitslip

value.

15:6

Reserved

UR0

10'b0

5

tx_

bitslip_

en

RW

1'b0

Enable manual

tx_bitslip_in

updates.

4:0

tx_

bitslip_

in

RW

5'b0

Number of bits of delay (bitslip) the CPRI v6.0 IP core adds at

the CPRI Tx link.

The CPRI line bit rate determines the following maximum

values for this field:

• Maximum value for IP core variations with CPRI line bit

rate 0.6144 Gbps: 9 bits.

• Maximum value for IP core variations with CPRI line bit

rate greater than 0.6144 Gbps: 19 bits.

5-20

XCVR_BITSLIP Register

UG-01156

2015.02.16

Altera Corporation

CPRI v6.0 IP Core Registers