Transceiver debug interface, Testing features, Cpri v6.0 ip core loopback modes – Altera CPRI v6.0 MegaCore Function User Manual

Page 79: Transceiver debug interface -49, Testing features -49, Cpri v6.0 ip core loopback modes -49

Transceiver Debug Interface

Table 3-28: Transceiver Debug Interface Signals

If you turn on Enable debug interface in the CPRI v6.0 parameter editor, the IP core provides some additional

status signals from the transceiver.

Signal Name

Direction

Description

xcvr_rx_is_lockedtoref

Output

Indicates that the receiver CDR is locked to the

xcvr_cdr_

refclk

reference clock.

xcvr_rx_is_lockedtodata

Output

Indicates that the receiver CDR is locked to the incoming

serial data.

xcvr_rx_errdetect[3:0]

Output

Each bit [n] indicates the receiver has detected an 8B/10B

code group violation in byte [n] of the 32-bit data word.

xcvr_rx_disperr[3:0]

Output

Each bit [n] indicates that the receiver has detected an 8B/

10B parity error in byte [n] of the 32-bit data word.

xcvr_rx_blk_sh_err

Output

Indicates that the receiver has detected a 64B/66B

SYNC_

HEADER

violation.

Testing Features

The CPRI v6.0 IP core supports multiple testing features.

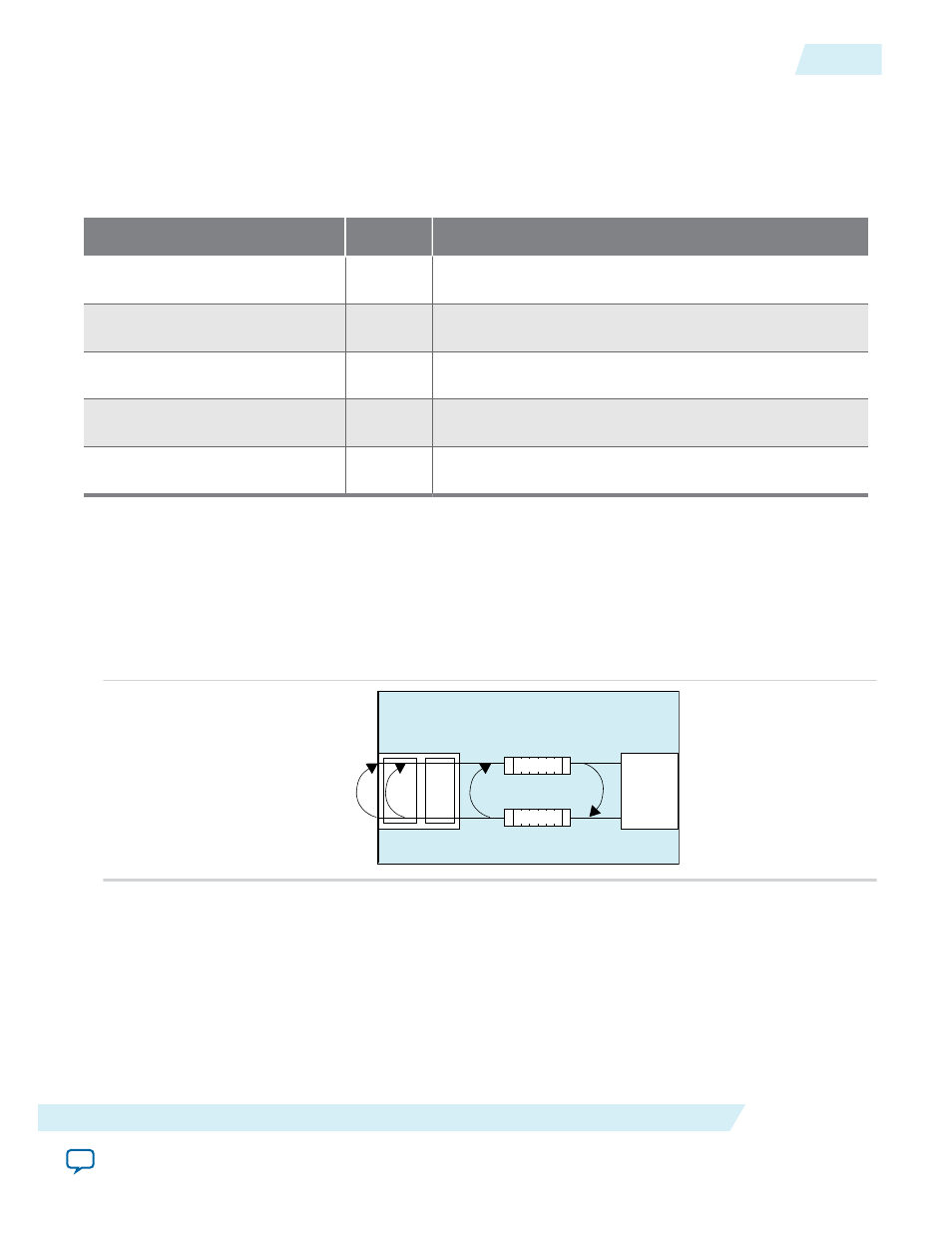

CPRI v6.0 IP Core Loopback Modes

Figure 3-28: CPRI v6.0 IP Core Loopback Modes

CPRI v6.0 IP Core

CPRI Link

(1)

(2)

(3)

(4)

Rx

PMA

Tx

CPRI Tx

CPRI Rx

PCS

UG-01156

2014.08.18

Transceiver Debug Interface

3-49

Functional Description

Altera Corporation