Cpri v6.0 ip core l1 direct access interfaces, Cpri v6.0 ip core l1 direct access interfaces -2 – Altera CPRI v6.0 MegaCore Function User Manual

Page 83

Signal Name

Direction

Interface

mii_tx_fifo_status[3:0]

Output

MII status signals

These signals are available only if you turn on Enable

IEEE 802.3 100BASE-X 100Mbps MII in the CPRI v6.0

parameter editor.

mii_rx_fifo_status[3:0]

Output

Related Information

Media Independent Interface (MII) to External Ethernet Block

Describes the MII signals and provides MII timing diagrams.

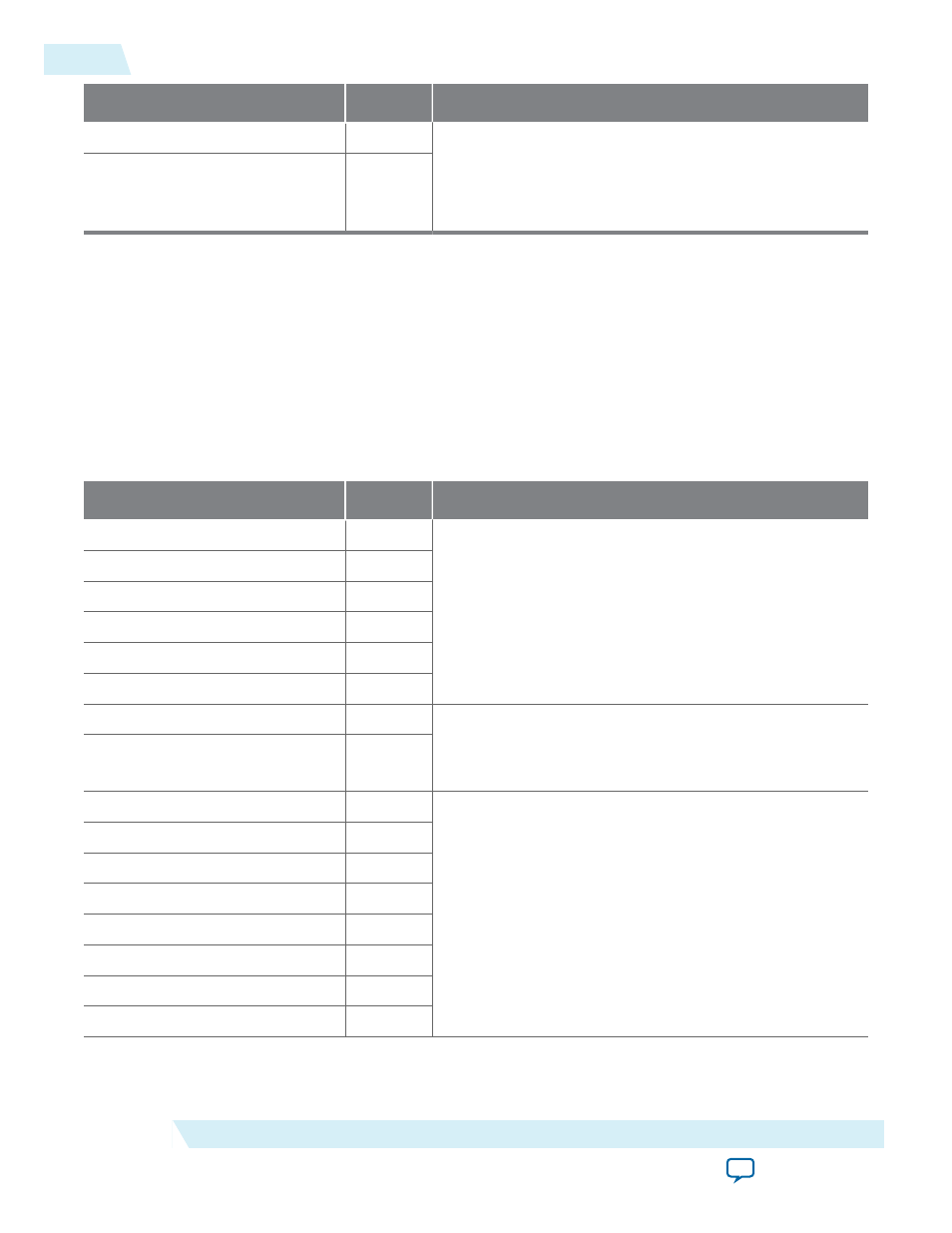

CPRI v6.0 IP Core L1 Direct Access Interfaces

The CPRI v6.0 IP core can communicate with the surrounding design through multiple optional

interfaces that provide direct access to all or part of the CPRI frame.

Table 4-2: L1 Direct Access Interface Signals

Signal Name

Direction

Description

aux_rx_rfp

Output

AUX RX interface status signals

These signals are available only if you turn on Enable

auxiliary interface in the CPRI v6.0 parameter editor.

aux_rx_hfp

Output

aux_rx_bfn[11:0]

Output

aux_rx_z[7:0]

Output

aux_rx_x[7:0]

Output

aux_rx_seq[6:0]

Output

aux_rx_data[31:0]

Output

AUX RX interface data signals

These signals are available only if you turn on Enable

auxiliary interface in the CPRI v6.0 parameter editor.

aux_rx_ctrl[3:0]

Output

aux_tx_sync_rfp

Input

AUX TX interface control and status signals

These signals are available only if you turn on Enable

auxiliary interface in the CPRI v6.0 parameter editor.

aux_tx_err[3:0]

Output

aux_tx_rfp

Output

aux_tx_hfp

Output

aux_tx_bfn[11:0]

Output

aux_tx_z[7:0]

Output

aux_tx_x[7:0]

Output

aux_tx_seq[6:0]

Output

4-2

CPRI v6.0 IP Core L1 Direct Access Interfaces

UG-01156

2014.08.18

Altera Corporation

CPRI v6.0 IP Core Signals