Cpu interface signals, Cpu interface signals -36 – Altera CPRI v6.0 MegaCore Function User Manual

Page 66

CPU Interface Signals

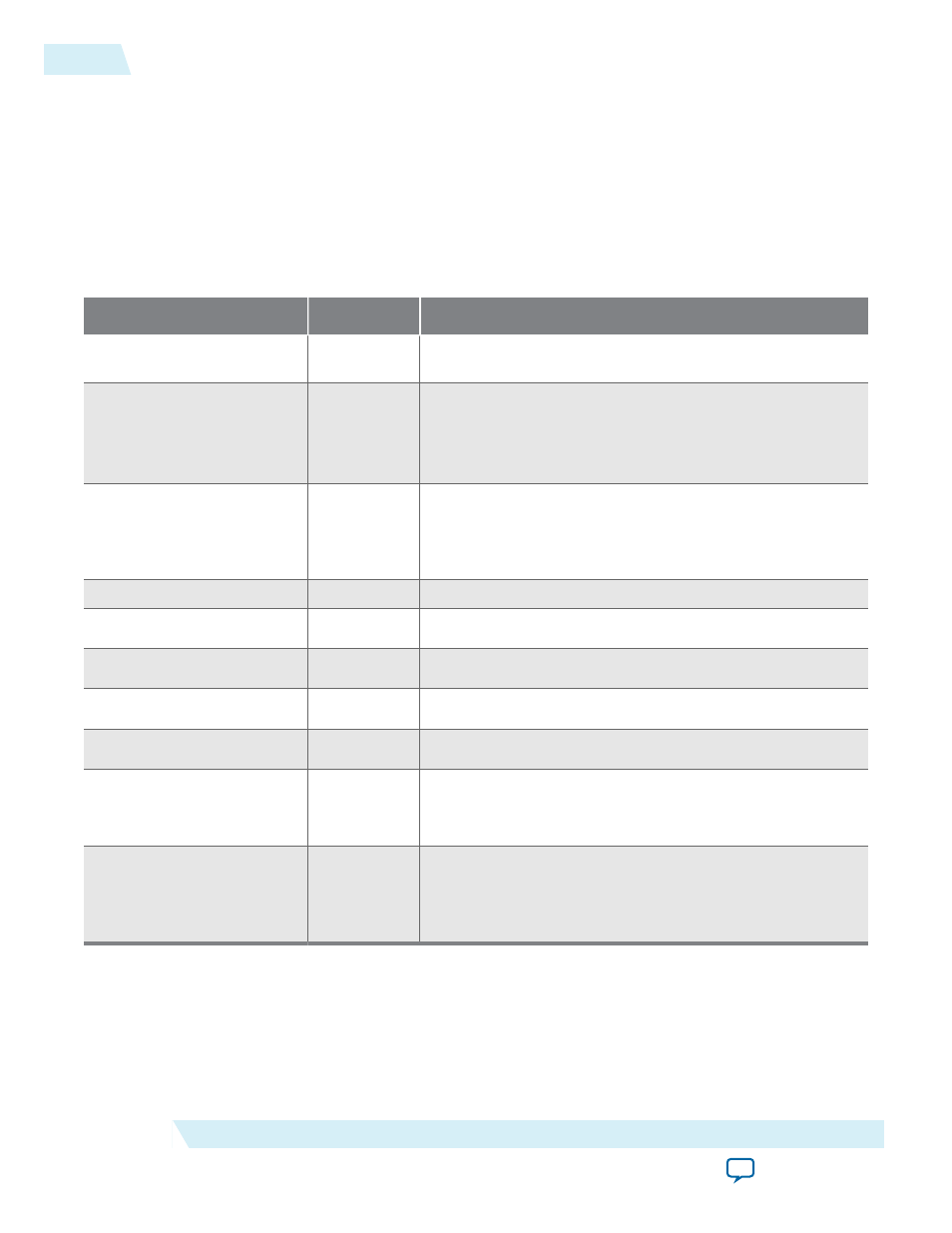

Table 3-12: CPRI v6.0 IP Core CPU Interface Signals

The CPRI v6.0 IP core CPU interface has the following features:

• Avalon-MM slave interface compliant.

• Provides support for single cycle read and write operations: you can read or write a single register in a single

access operation.

• Supports a single

cpu_clk

clock cycle read latency and a zero

cpu_clk

clock cycle write latency for most

registers.

Signal Name

Direction

Description

cpu_clk

Input

Clocks the signals on the CPRI v6.0 CPU interface. Supports

any frequency that the device fabric supports.

cpu_reset

Input

Active low reset signal. Resets the CPRI v6.0 CPU interface

and all of the registers to which it provides access.

You should hold this signal asserted for one full

cpu_clk

cycle to ensure it is captured by the IP core.

cpu_address[15:0]

Input

Address for reads and writes. All CPRI v6.0 control and

status registers are 32 bits wide. Therefore, this address is a

word address (addresses a 4-byte (32-bit) word), not a byte

address.

cpu_byteenable[3:0]

Input

Data-byte enable signal

cpu_read

Input

You must assert this signal to request a read transfer

cpu_write

Input

You must assert this signal to request a write transfer

cpu_writedata[31:0]

Input

Write data

cpu_readdata[31:0]

Output

Read data

cpu_waitrequest

Output

Indicates that the control and status interface is busy

executing an operation. When the IP core deasserts this

signal, the operation is complete and the read data is valid.

cpu_irq

Output

Interrupt request. All interrupts that you enable in the

relevant register fields, assert this interrupt signal when they

are triggered. You must check the relevant register fields to

determine the cause or causes of the interrupt assertion.

Related Information

For more information about the Avalon-MM protocol, including timing diagrams, refer to the Avalon

Memory-Mapped Interfaces chapter.

3-36

CPU Interface Signals

UG-01156

2014.08.18

Altera Corporation

Functional Description