Altera CPRI v6.0 MegaCore Function User Manual

Page 88

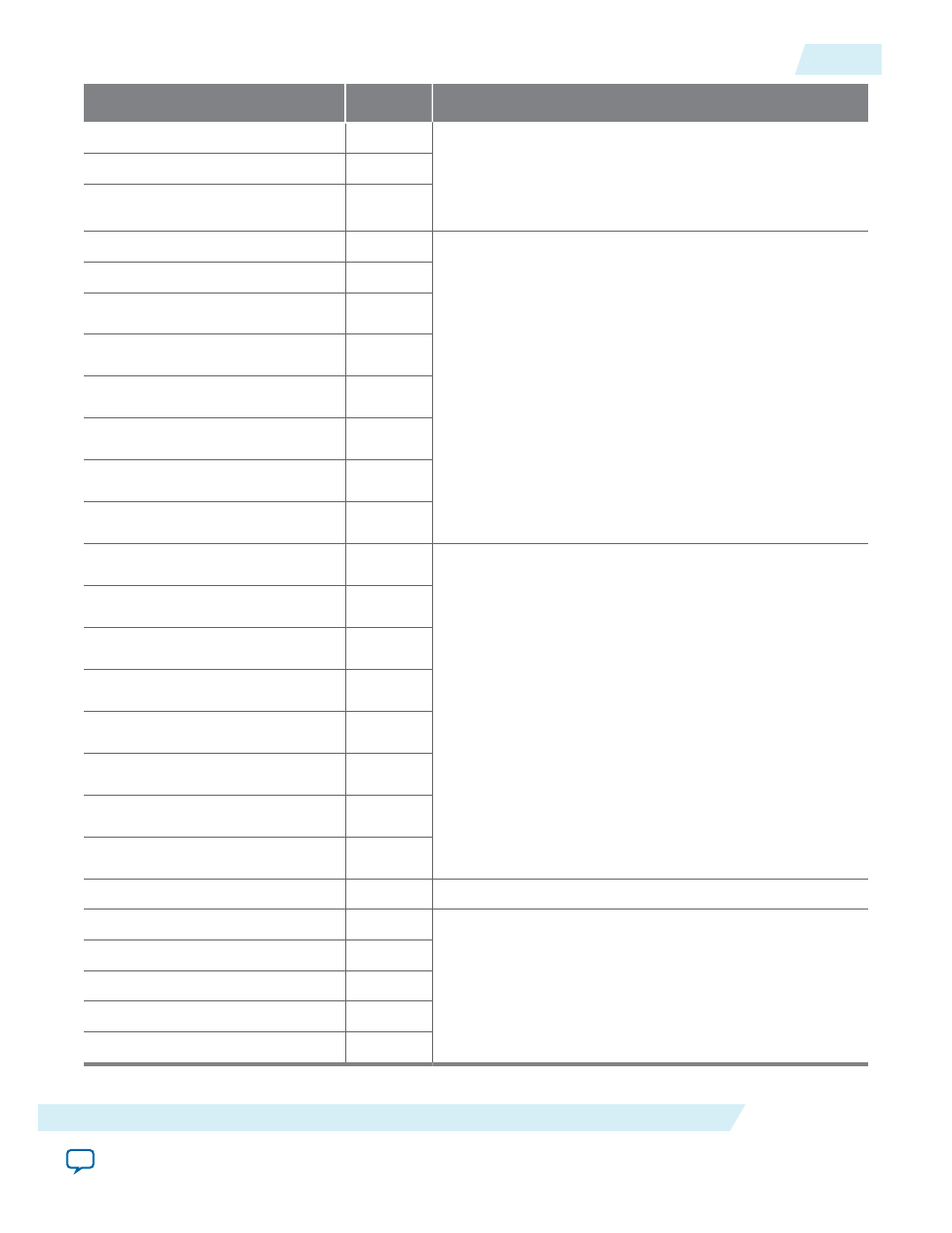

Signal Name

Direction

Description

reconfig_clk

Input

Arria V GZ and Stratix V transceiver reconfiguration

interface

These signals are present only in P core variations that

target an Arria V GZ or Stratix V device.

reconfig_to_xcvr[69:0]

Input

reconfig_from_xcvr[45:0]

Output

reconfig_clk

Input

Arria 10 transceiver reconfiguration interface

These signals are present only in P core variations that

target an Arria 10 device.

reconfig_reset

Input

reconfig_write

Input

reconfig_read

Input

reconfig_address[9:0]

Input

reconfig_writedata[31:0]

Input

reconfig_readdata[31:0]

Output

reconfig_waitrequest

Output

xcvr_tx_analogreset

Input

Interface to external reset controller

xcvr_tx_digitalreset

Input

xcvr_tx_cal_busy

Output

xcvr_rx_analogreset

Input

xcvr_rx_digitalreset

Input

xcvr_rx_cal_busy

Output

xcvr_reset_tx_ready

Input

xcvr_reset_rx_ready

Input

xcvr_ext_pll_clk

Input

Interface to external TX PLL

xcvr_rx_is_lockedtoref

Output

Transceiver debug interface

These signals are present only if you turn on Enable

debug interface in the CPRI v6.0 parameter editor.

xcvr_rx_is_lockedtodata

Output

xcvr_rx_errdetect[3:0]

Output

xcvr_rx_disperr[3:0]

Output

xcvr_rx_blk_sh_err

Output

UG-01156

2014.08.18

CPRI v6.0 IP Core Transceiver and Transceiver Management Signals

4-7

CPRI v6.0 IP Core Signals

Altera Corporation