Altera CPRI v6.0 MegaCore Function User Manual

Page 61

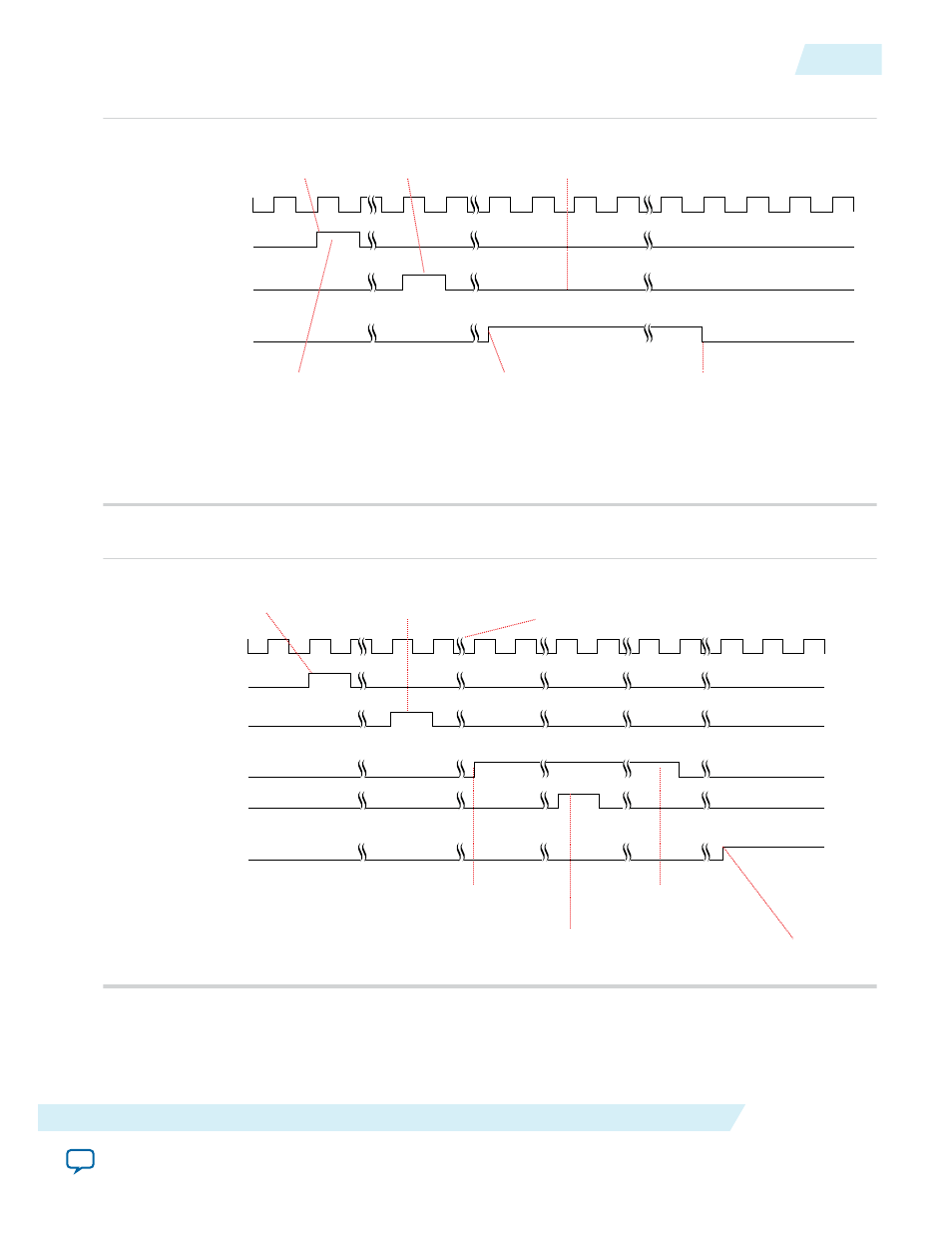

Figure 3-22: sdi_assert to sdi_req on Direct L1 Control and Status Interface

cpri_clkout

Master z130_sdi_assert

DL Frame Z.130.0[2] (Internal)

Slave z130_sdi_req

Assert for at Least One Clock

Cycle to Ensure at Least One

Hyperframe Z.13.0[2] Asserted

Nearest

Z.130.0 Bit [2]

Next Z.130.0 Bit [2]

Is Not Asserted

For Longer Slave sdi_req Assertion

(More than One Hyperframe),

Hold sdl_assert for More than One

Hyperframe or Assert for One

Clock Cycle 3 Clock Cycles before

Z.130.0 (See AUX Status

Signals) at Each Hyperframe

Assertion after Detecting the

First Z.130.0[2] Assertion

Hold Assertion for One

Hyperframe until the

Next Z.130.0[2] Detection

Figure 3-23: reset_assert to reset_req on Direct L1 Control and Status Interface

cpri_clkout

Master z130_reset_assert

DL Frame Z.130.0[0] (Internal)

Slave z130_reset_req

Assert for at Least One Clock

Cycle to Ensure at Least One

Hyperframe Z.13.0[2] Asserted

Nearest Next 10 Hyperframe

Z.130.0 Bit [0] Is Asserted

Automatically

After Another Nine

Hyperframes

Assertion after Detecting the

Tenth Z.130.0[2] Assertion

Hold Assertion for at

Least One Hyperframe

Slave Sends Next Five Hyperframes

of Z.130.0[0] for Acknowledgement

Acknowledgement Signal Hold

for at Least One Hyperframe

UL Frame Z.130.0[0] (Internal)

Master z130_reset_req

UG-01156

2014.08.18

Direct L1 Control and Status Interface

3-31

Functional Description

Altera Corporation