Altera CPRI v6.0 MegaCore Function User Manual

Page 74

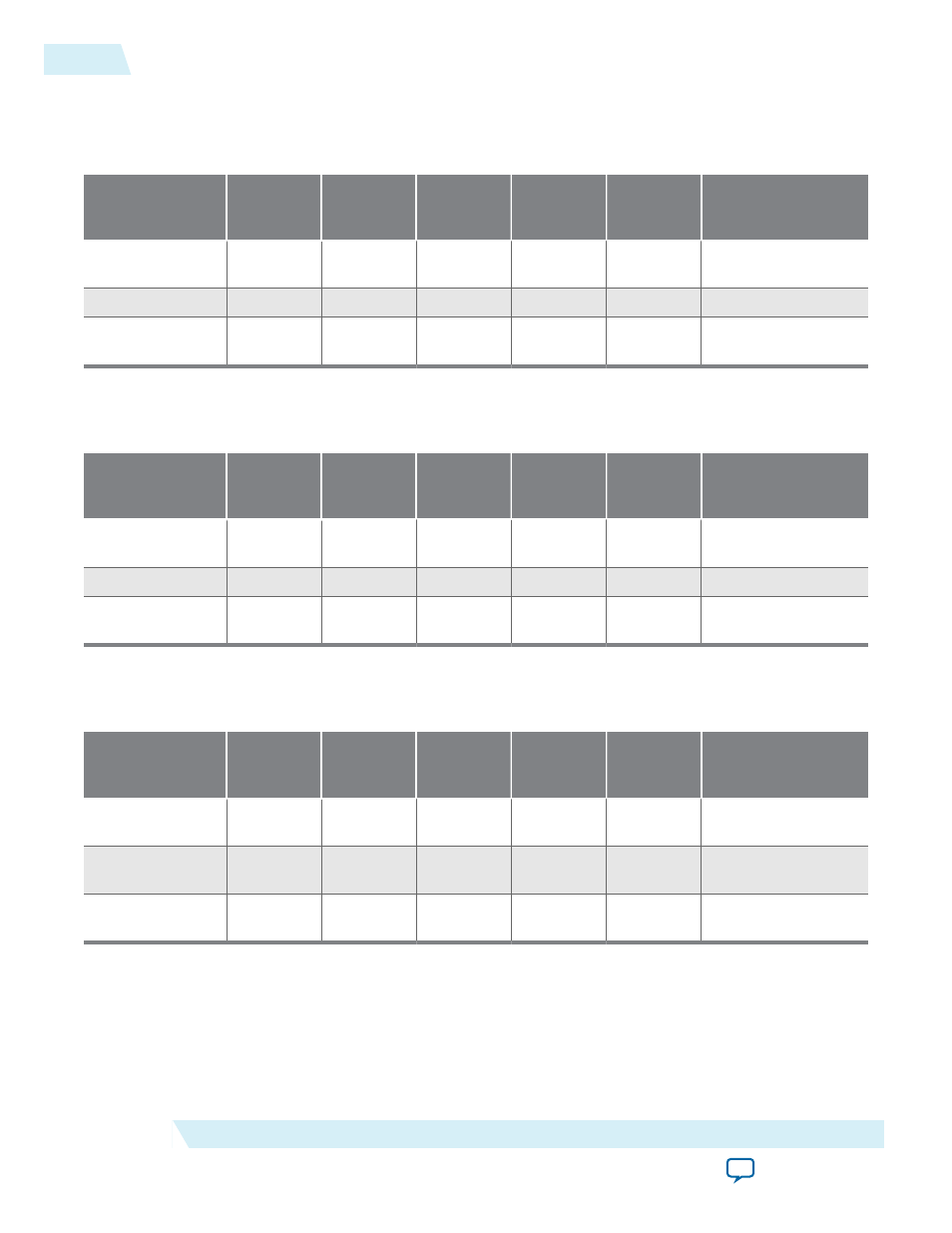

Table 3-18: Delays on Transmit Path Through CPRI v6.0 IP Core in Arria 10 Devices

In this table, P1 is the duration of one

cpri_clkout

clock cycle, and P2 is the duration of one TX PCS clock cycle.

tx_ex_delay is the value in the

tx_ex_delay

field of the TX_EX_DELAY register at offset 0x50. B2 is the number

of bits in a TX PCS clock cycle.

CPRI Line Bit Rate

(Gbps)

Bits per

cpri_clkout

Cycle

Bits per TX

PCS Clock

Cycle (=B2)

From AUX

TX Interface

to TX Buffer

Through TX

Buffer

Through

PCS

Through PMA

0.6144

32

10

(5 x P1) +

P2

tx_ex_delay 5 x P2

(3 x P2) + (2 x P2/

B2)

1.2288–9.8304 32

40

6 x P1

tx_ex_delay 4 x P2

32 x P2/B2

10.1376

32

40

(7 x P1) +

P2

tx_ex_delay

x 2

9 x P2

32 x P2/B2

Table 3-19: Delays on Receive Path Through CPRI v6.0 IP Core in Arria 10 Devices

In this table, P1 is the duration of one

cpri_clkout

clock cycle, and P2 is the duration of one RX PCS clock cycle.

rx_ex_delay is the value in the

rx_ex_delay

field of the RX_EX_DELAY register at offset 0x54.

CPRI Line Bit Rate

(Gbps)

Bits per

cpri_clkout

Cycle

Bits per RX

PCS Clock

Cycle (=B2)

Through

PMA

Through

PCS

Through RX

Buffer

From RX Buffer to AUX

RX Interface

0.6144

32

10

(2 x P2) +

(6 x P2/B2)

6 x P2

rx_ex_delay (7 x P1) + P2

1.2288–9.8304 32

40

31 x P2/B2 9 x P2

rx_ex_delay 8 x P1

10.1376

32

40

31 x P2/B2 5 x P2

rx_ex_delay

x 2

(7 x P1) + P2

Table 3-20: Delays on Transmit Path Through CPRI v6.0 IP Core in Stratix V Devices

In this table, P1 is the duration of one

cpri_clkout

clock cycle, and P2 is the duration of one TX PCS clock cycle.

tx_ex_delay is the value in the

tx_ex_delay

field of the TX_EX_DELAY register at offset 0x50.

CPRI Line Bit Rate

(Gbps)

Bits per

cpri_clkout

Cycle

Bits per TX

PCS Clock

Cycle (=B2)

From AUX

TX Interface

to TX Buffer

Through TX

Buffer

Through

PCS

Through PMA

0.6144

32

10

(5 x P1) +

P2

tx_ex_delay 3 x P2

(5 x P2) + (2 x P2/

B2)

1.2288–9.8304 32

40

6 x P1

tx_ex_delay 2 x P2

(2 x P2) + (3 x P2/

B2)

10.1376

32

40

(7 x P1) +

P2

tx_ex_delay

x 2

6 x P2

(2 x P2) + (3 x P2/

B2)

3-44

Deterministic Latency

UG-01156

2014.08.18

Altera Corporation

Functional Description