Fpga programming over external usb-blaster, Status elements, Status leds – Altera Stratix V Advanced Systems Development Board User Manual

Page 28: Fpga programming over external usb-blaster –18, Status elements –18, Status leds –18

2–18

Chapter 2: Board Components

Configuration, Status, and Setup Elements

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

f

For more information about the AS configuration mode, refer to the

pter in the Stratix V

Handbook.

FPGA Programming over External USB-Blaster

The JTAG programming header provides another method for configuring the FPGA

using an external USB-Blaster device with the Quartus II Programmer running on a

PC. The external USB-Blaster connects to the board through the JTAG header (J11).

When you install the external USB-Blaster into the JTAG header, the on-board

USB-Blaster II device is automatically disabled to prevent contention between these

two JTAG masters.

f

For more information on the following topics, refer to the respective documents:

■

SFL megafunction, refer to

■

PFL megafunction, refer to

Status Elements

The development board includes board-specific status LEDs and switches for

enabling and configuring various features on the board. This section describes these

status elements.

Status LEDs

Surface mount LEDs indicate various status of the board. A logic 0 is driven on the

I/O port to turn on the LED while a logic 1 is driven to turn off the LED.

lists the LED board references, names, and functional descriptions.

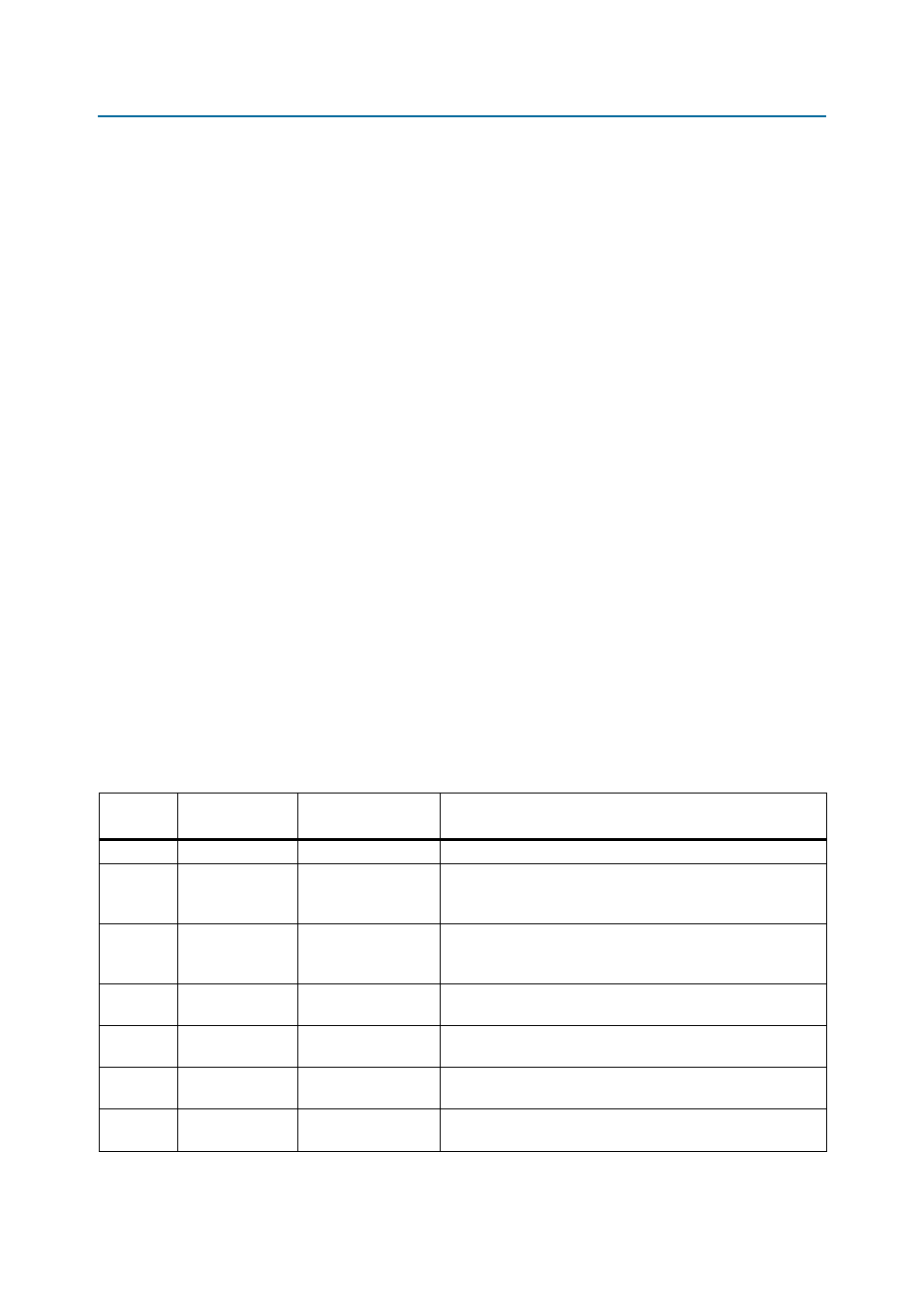

Table 2–8. Board-Specific LEDs (Part 1 of 2)

Board

Reference

LED Name

Schematic Signal

Name

Description

D27

PWR

—

Blue LED. Illuminates when 5.0-V power is active.

D14

ERROR

MAX_ERROR

Red LED. Illuminates when the MAX V CPLD System Controller

fails to configure the FPGA. Driven by the MAX V CPLD System

Controller.

D12

LOAD

MAX_LOAD

Green LED. Illuminates when the MAX V CPLD System Controller

is actively configuring the FPGA. Driven by the MAX V CPLD

System Controller.

D13

CONF_DONE

MAX_CONF_DONEn

Green LED. Illuminates when the FPGA is successfully

configured. Driven by the MAX V CPLD System Controller.

D34

FMC_RX

FMC_RX_LED

Green LED. Blinks to indicate FMC receive activity. Driven by

FPGA1.

D35

FMC_TX

FMC_TX_LED

Green LED. Blinks to indicate FMC transmit activity. Driven by

FPGA1.

D36

FMC_PRSNTn

FMC_PRSNTn

Green LED. Illuminates when the FMC is installed. Driven by the

FMC.