Altera Arria V Avalon-MM User Manual

Page 162

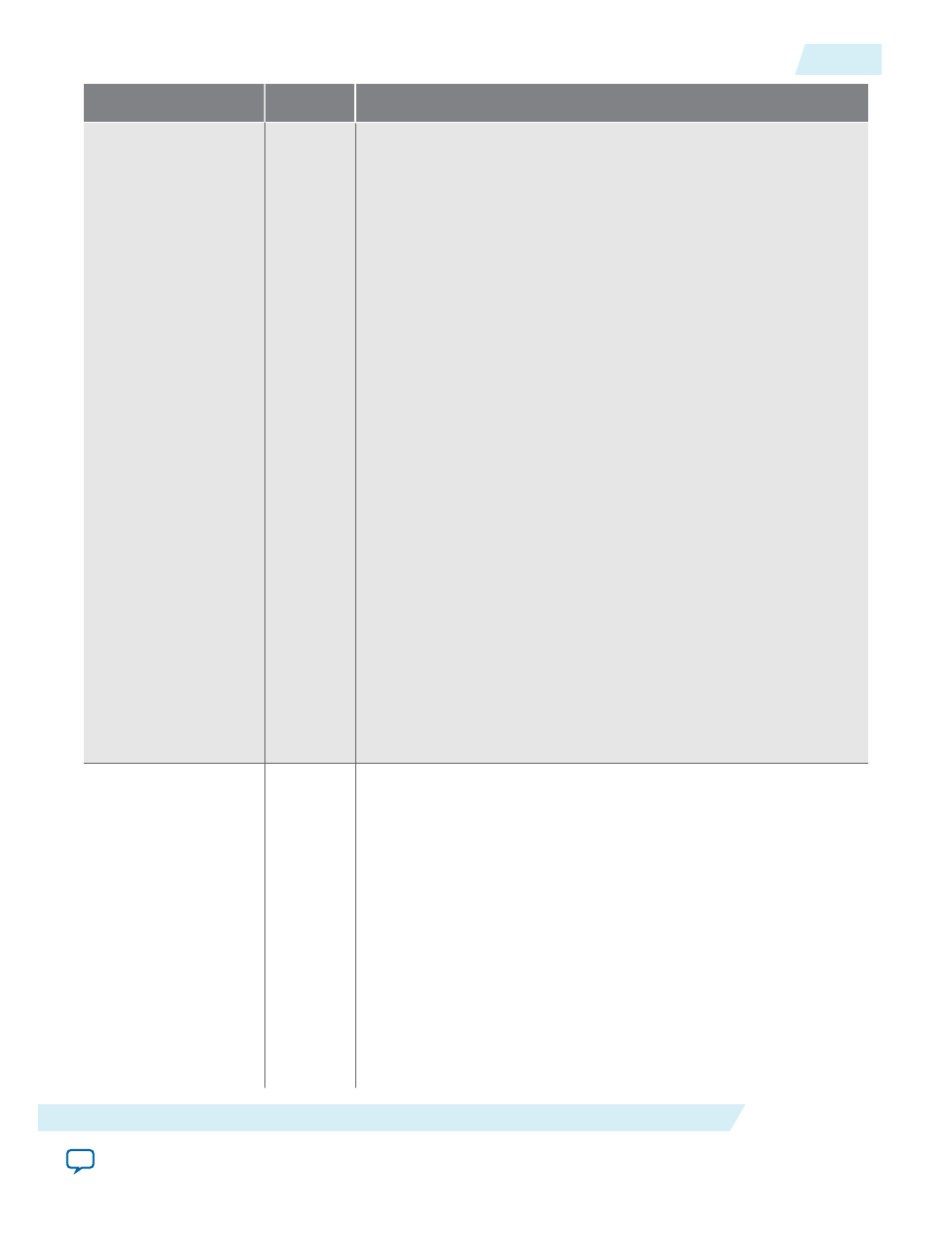

Date

Version

Changes Made

• Clarified that the Avalon-MM Bridge does not generate out-of-

order Avalon-MM-to-PCI Express Read Completions even to

different BARs.

• Removed

reconfig_busy

port from connect between PHY IP

Core for PCI Express and the Transceiver Reconfiguration

Controller in the Altera Transceiver Reconfiguration Controller

Connectivity figure. The Transceiver Reconfiguration Controller

drives

reconfig_busy

port to the Altera PCIe Reconfig Driver.

• Added fact that DCD calibration is required for Gen2 data rate in

the description of the transceiver reconfiguration signals. Updated

figure showing Transceiver Reconfiguration Controller parameter

editor.

• Removed reference to Gen2 x1 62.5 MHz configuration in

Application Layer Clock Frequency for All Combination of Link

Width, Data Rate and Application Layer Interface Widths table.

This configuration is not supported.

• Added description of

TxsWaitRequest

signal which is asserted

when the Avalon-MM bridge has eight outstanding read requests.

• Added sections on making analog QSF and pin assignments.

• Enhanced definition of Device ID and Sub-system Vendor ID to

say that these registers are only valid in the Type 0 (Endpoint)

Configuration Space.

• Improved figure showing multiple MSI and MSI-X support and

added reference to example on Altera wiki.

• Removed references to the ATX PLL. This PLL is not available for

Arria V

• Updated Power Supply Voltage Requirements table.

• For Cyclone V devices changed speed grade recommendation to

use GT devices for both the Gen1 and Gen2 data rate.

2014.12.20

13.1

Made the following changes:

• Added constraints for

refclk

when CvP is enabled.

• Corrected location information for

nPERSTL*

.

• Corrected definition of

test_in[4:1]

.

• In Debugging chapter, under changing between soft and hard reset

controller, changed the file name in which the parameter

hip_

hard_reset_hwtcl

must be set to 0 to use the soft reset controller.

• Added explanation of channel labeling for serial data. The Hard IP

on the left side of the device must connect to the appropriate

channels on the left side of the device, and so on.

• Corrected connection for the Transceiver Reconfiguration

Controller IP Core reset signal,

alt_xcvr_reconfig_0 mgmt_

rst_reset

, Getting Started with the Avalon-MM Arria V Hard IP

for PCI Express. This reset input connects to

clk_0 clk_reset

.

UG-01105_avmm

2014.08.18

Revision History for the Avalon-MM Interface

C-3

Additional Information

Altera Corporation