Hard ip status – Altera Arria V Avalon-MM User Manual

Page 40

Signal

Direction

Description

even if the V

VCCPGM

of the bank is not 3.3V if the following 2

conditions are met:

• The input signal meets the V

IH

and V

IL

specification for

LVTTL.

• The input signal meets the overshoot specification for 100°C

operation as specified by the “Maximum Allowed Overshoot

and Undershoot Voltage” in the Device Datasheet for Arria V

Devices.

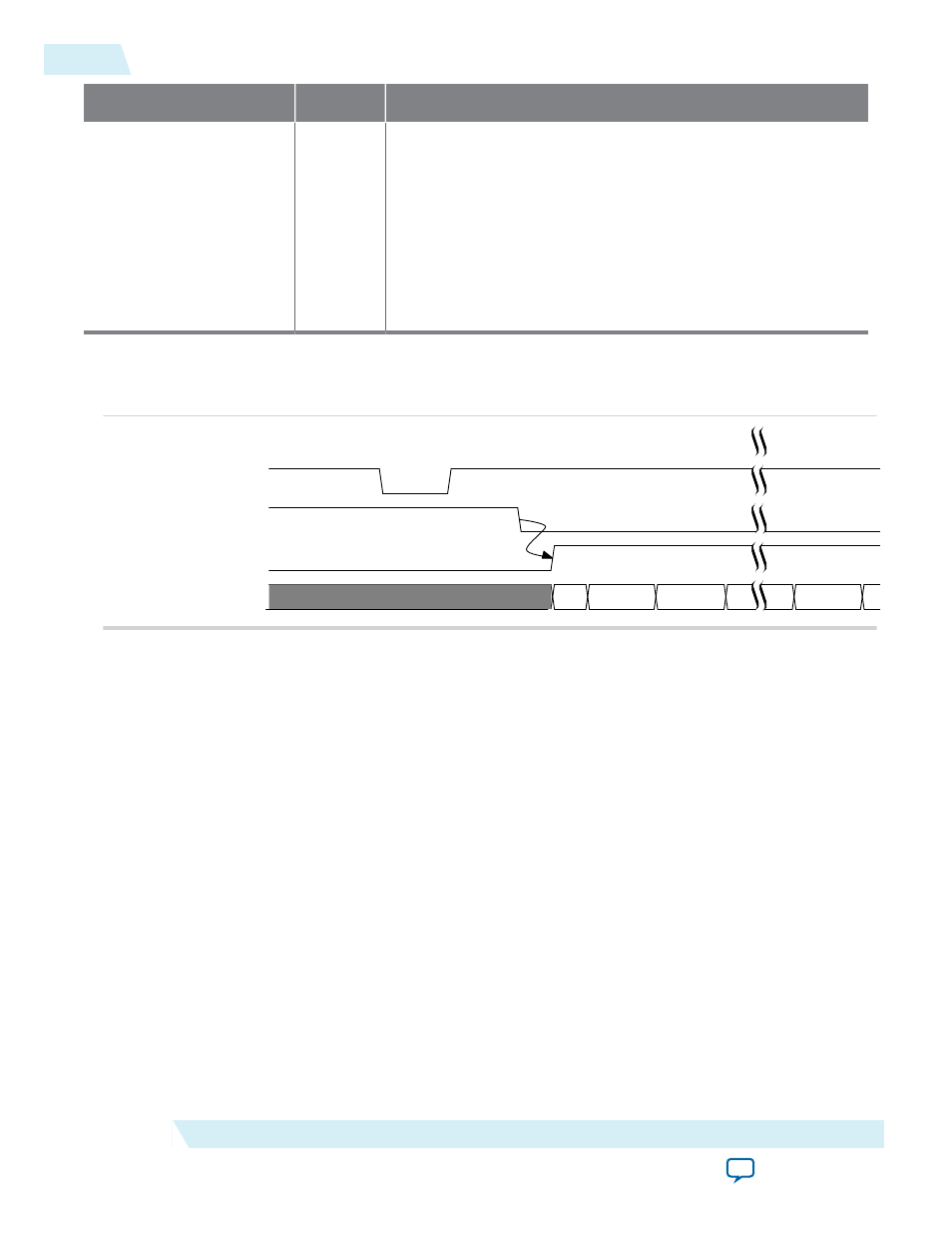

Figure 4-2: Reset and Link Training Timing Relationships

The following figure illustrates the timing relationship between

npor

and the LTSSM L0 state.

npor

IO_POF_Load

PCIe_LinkTraining_Enumeration

dl_ltssm[4:0]

detect detect.active polling.active

L0

Note: To meet the 100 ms system configuration time, you must use the fast passive parallel configuration

scheme with and a 32-bit data width (FPP x32).

Related Information

•

•

Hard IP Status

Refer to Reset and Clocks for more information about the reset sequence and a block diagram of the reset

logic.

4-10

Hard IP Status

UG-01105_avmm

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions