Uncorrectable internal error status register – Altera Arria V Avalon-MM User Manual

Page 95

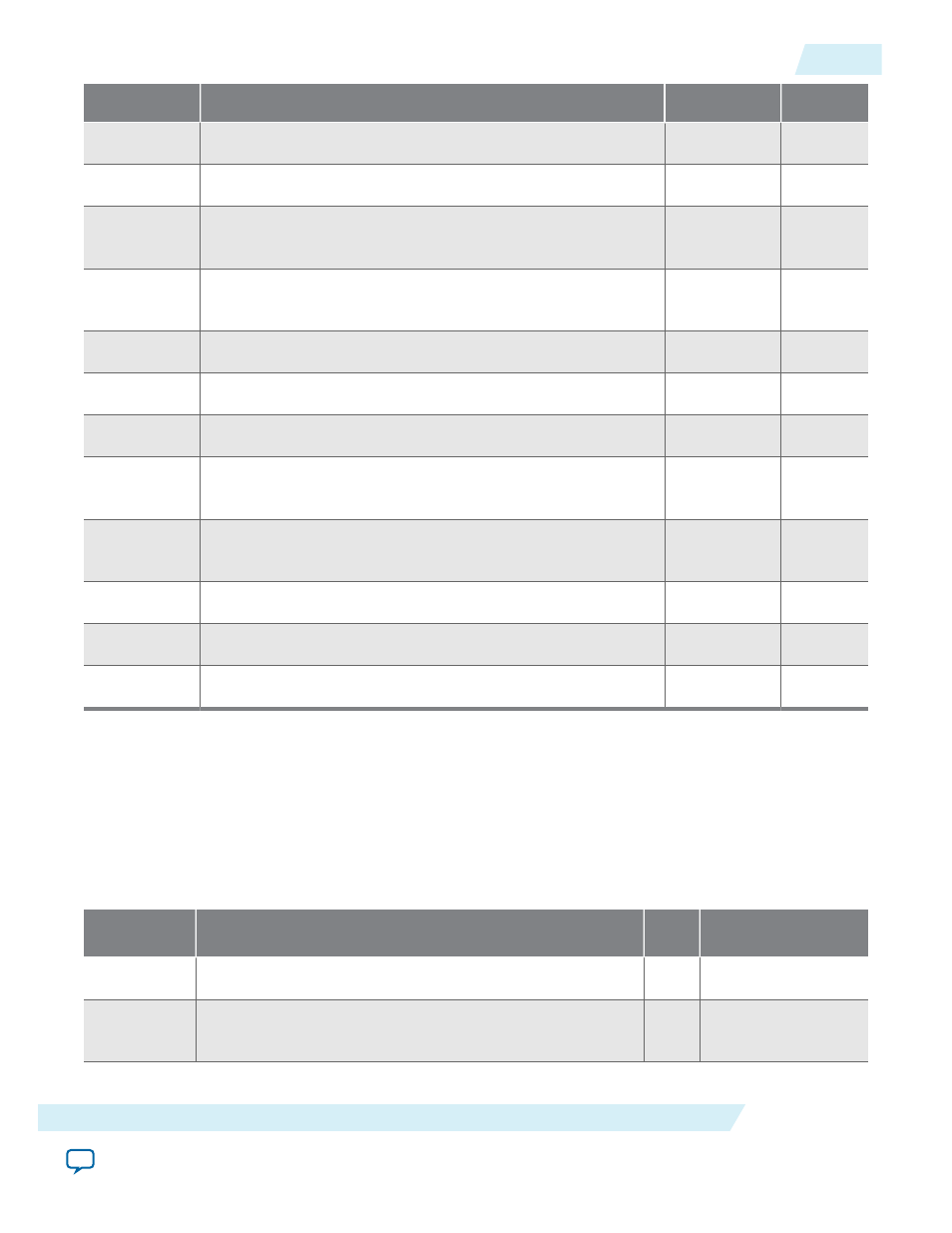

Bits

Register Description

Reset Value

Access

[11]

Mask for RX buffer posted and completion overflow error.

1b’1

RWS

[10]

Reserved

1b’0

RO

[9]

Mask for parity error detected on Configuration Space to TX bus

interface.

1b’1

RWS

[8]

Mask for parity error detected on the TX to Configuration Space

bus interface.

1b’1

RWS

[7]

Mask for parity error detected at TX Transaction Layer error.

1b’1

RWS

[6]

Reserved

1b’0

RO

[5]

Mask for configuration errors detected in CvP mode.

1b’0

RWS

[4]

Mask for data parity errors detected during TX Data Link LCRC

generation.

1b’1

RWS

[3]

Mask for data parity errors detected on the RX to Configuration

Space Bus interface.

1b’1

RWS

[2]

Mask for data parity error detected at the input to the RX Buffer.

1b’1

RWS

[1]

Mask for the retry buffer uncorrectable ECC error.

1b’1

RWS

[0]

Mask for the RX buffer uncorrectable ECC error.

1b’1

RWS

Uncorrectable Internal Error Status Register

Table 5-28: Uncorrectable Internal Error Status Register

This register reports the status of the internally checked errors that are uncorrectable. When specific errors are

enabled by the

Uncorrectable Internal Error Mask

register, they are handled as Uncorrectable Internal

Errors as defined in the PCI Express Base Specification 3.0. This register is for debug only. It should only be used to

observe behavior, not to drive custom logic. The access code RW1CS represents Read Write 1 to Clear Sticky.

Bits

Register Description

Reset

Value

Access

[31:12]

Reserved.

0

RO

[11]

When set, indicates an RX buffer overflow condition in a

posted request or Completion

0

RW1CS

UG-01105_avmm

2014.12.15

Uncorrectable Internal Error Status Register

5-33

Registers

Altera Corporation