Altera Arria V Avalon-MM User Manual

Page 43

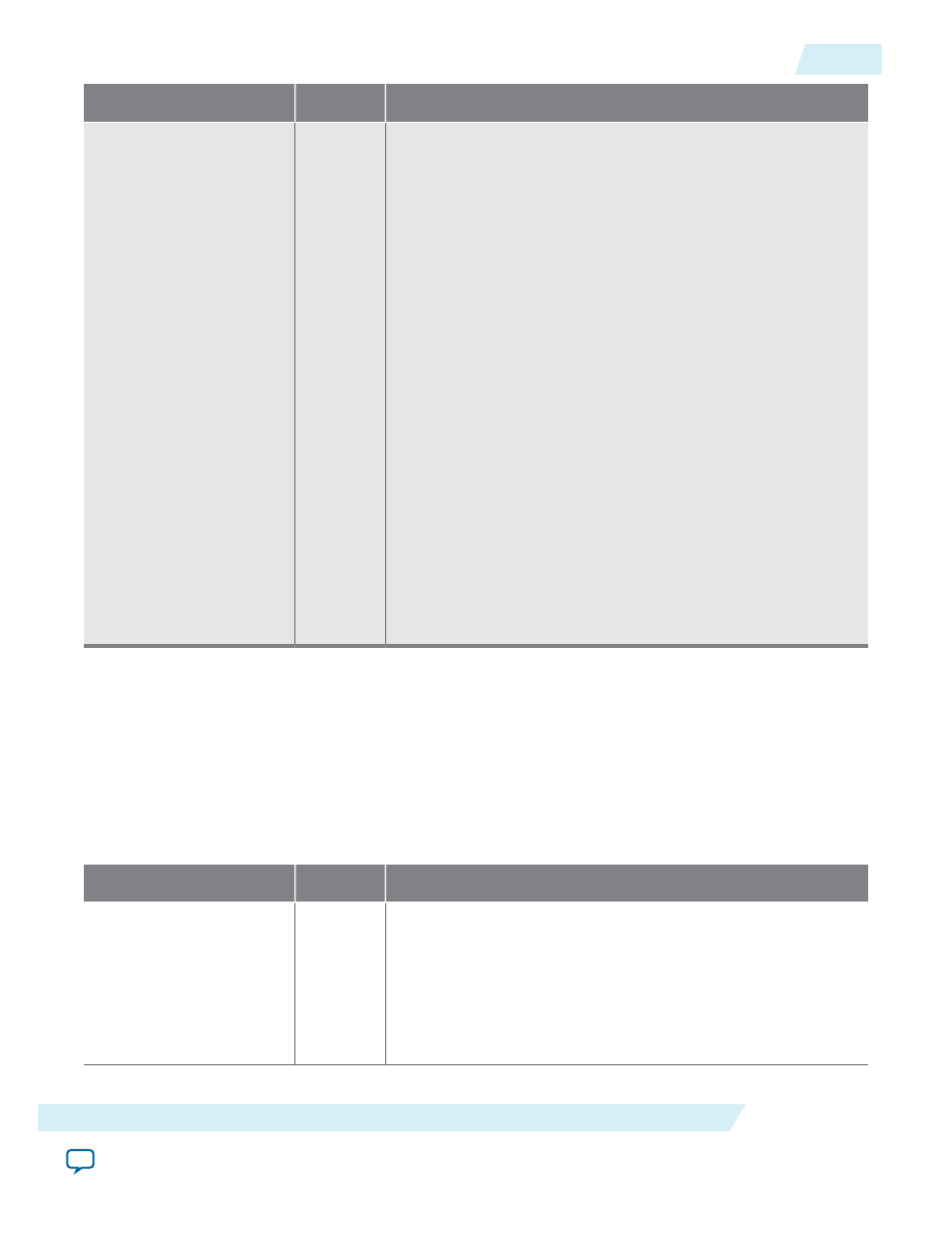

Signal

Direction

Description

• 00110: config.Linkwidthstart

• 00111: Config.Linkaccept

• 01000: Config.Lanenumaccept

• 01001: Config.Lanenumwait

• 01010: Config.Complete

• 01011: Config.Idle

• 01100: Recovery.Rcvlock

• 01101: Recovery.Rcvconfig

• 01110: Recovery.Idle

• 01111: L0

• 10000: Disable

• 10001: Loopback.Entry

• 10010: Loopback.Active

• 10011: Loopback.Exit

• 10100: Hot.Reset

• 10101: LOs

• 11001: L2.transmit.Wake

• 11010: Speed.Recovery

• 11011: Recovery.Equalization, Phase 0

• 11100: Recovery.Equalization, Phase 1

• 11101: Recovery.Equalization, Phase 2

• 11110: recovery.Equalization, Phase 3

Related Information

Interrupts for Endpoints when Multiple MSI/MSI‑X Support Is Enabled

Table 4-7: Exported Interrupt Signals for Endpoints when Multiple MSI/MSI‑X Support is Enabled

The following table describes the IP core’s exported interrupt signals when you turn on Enable multiple MSI/

MSI-X support under the Avalon-MM System Settings banner in the parameter editor.

Signal

Direction

Description

MsiIntfc_o[81:0]

Output

This bus provides the following MSI address, data, and enabled

signals:

•

MsiIntf_o[81]

: Master enable

•

MsiIntf_o[80

}: MSI enable

•

MsiIntf_o[79:64]

: MSI data

•

MsiIntf_o[63:0]

: MSI address

UG-01105_avmm

2014.12.15

Interrupts for Endpoints when Multiple MSI/MSI‑X Support Is Enabled

4-13

Interfaces and Signal Descriptions

Altera Corporation