Hard ip status extension – Altera Arria V Avalon-MM User Manual

Page 46

The ×8 variants require an extra channel for PCS clock routing and control. The ×8 variants use channel 4

for clocking.

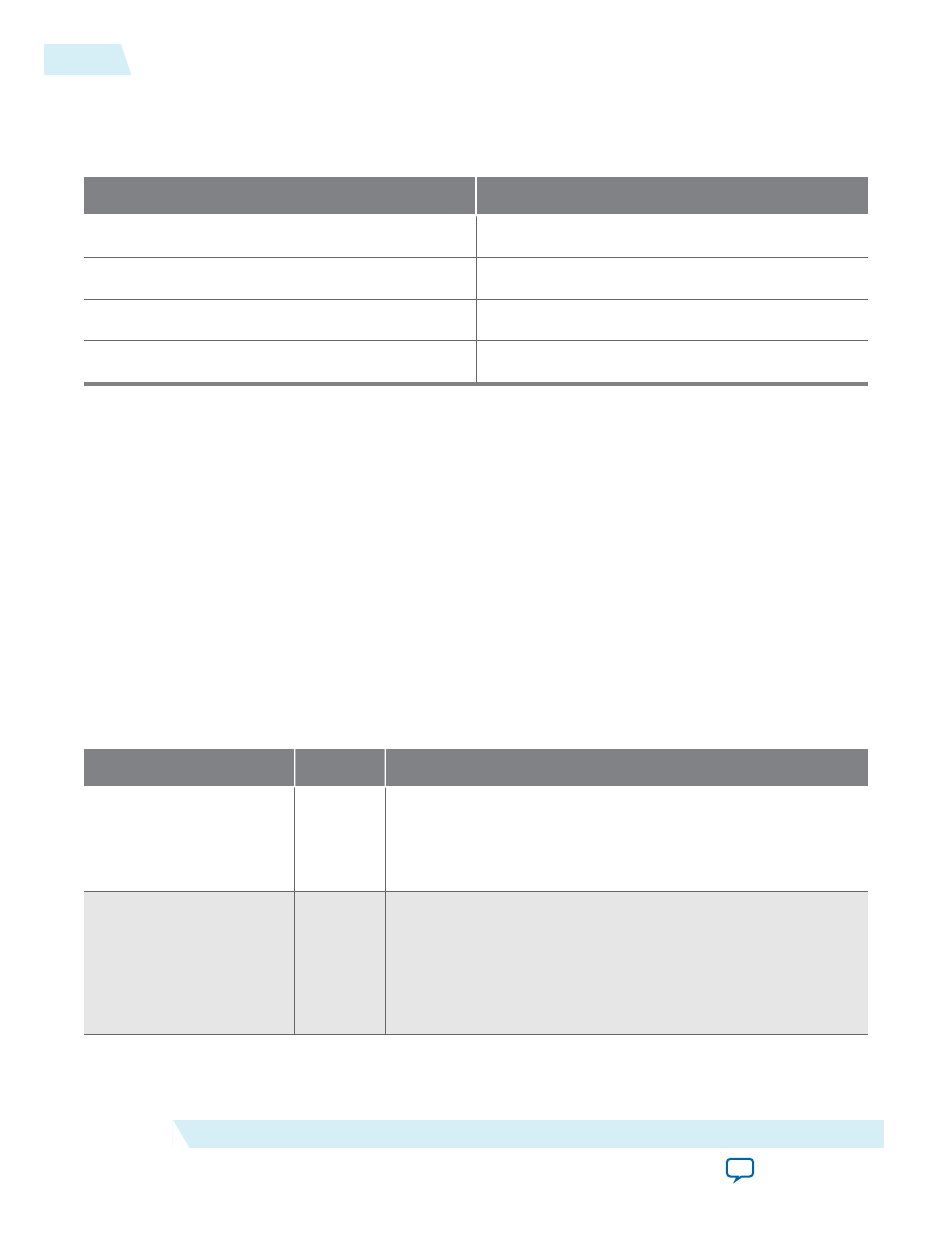

Table 4-9: Number of Logical and Physical Reconfiguration Interfaces

Variant

Logical Interfaces

Gen1 and Gen2 ×1

2

Gen1 and Gen2 ×2

3

Gen1 and Gen2 ×4

5

Gen1 ×8

10

For more information about the Transceiver Reconfiguration Controller, refer to the Transceiver Reconfi‐

guration Controller chapter in the Altera Transceiver PHY IP Core User Guide .

Related Information

Hard IP Status Extension

Table 4-10: Hard IP Status Extension Signals

This optional bus adds signals that are useful for debugging to the top-level variant, including:

• The most important native Avalon-ST RX signals

• The Configuration Space signals

• The BAR

• The ECC error

• The signal indicating that the

pld_clk

is in use

Signal

Direction

Description

pld_clk_inuse

Output

When asserted, indicates that the Hard IP Transaction Layer is

using the

pld_clk

as its clock and is ready for operation with the

Application Layer. For reliable operation, hold the Application

Layer in reset until

pld_clk_inuse

is asserted.

pme_to_sr

Output

Power management turn off status register.

Root Port—This signal is asserted for 1 clock cycle when the Root

Port receives the

pme_turn_off

acknowledge message.

Endpoint—This signal is asserted for 1 cycle when the Endpoint

receives the

PME_turn_off

message from the Root Port.

4-16

Hard IP Status Extension

UG-01105_avmm

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions