Altera Arria V Avalon-MM User Manual

Page 47

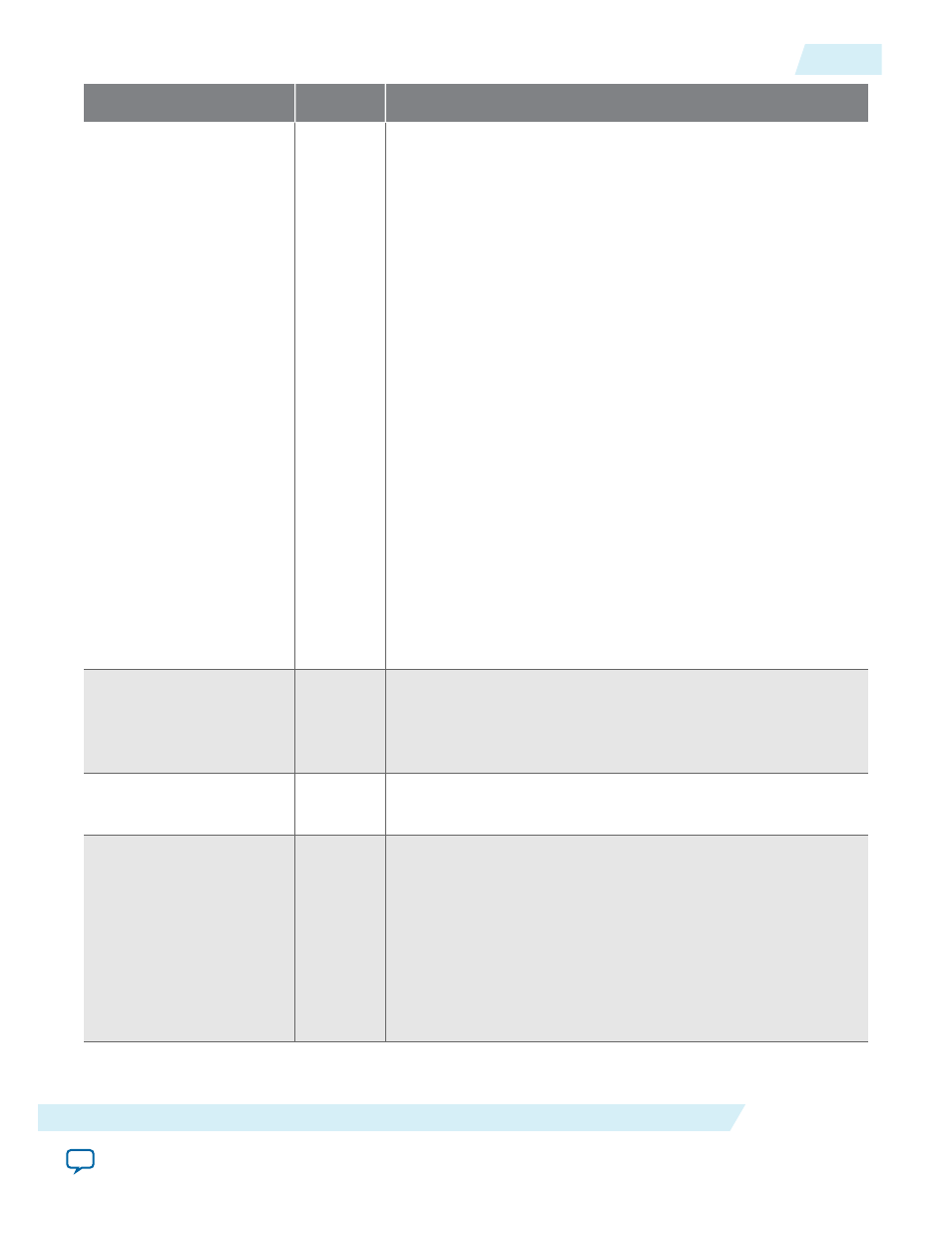

Signal

Direction

Description

rx_st_bar[7:0]

Output

The decoded BAR bits for the TLP. Valid for

MRd

,

MWr

,

IOWR

, and

IORD

TLPs. Ignored for the completion or message TLPs. Valid

during the cycle in which

rx_st_sop

is asserted.

The following encodings are defined for Endpoints:

• Bit 0: BAR 0

• Bit 1: BAR 1

• Bit 2: Bar 2

• Bit 3: Bar 3

• Bit 4: Bar 4

• Bit 5: Bar 5

• Bit 6: Reserved

• Bit 7: Reserved

The following encodings are defined for Root Ports:

• Bit 0: BAR 0

• Bit 1: BAR 1

• Bit 2: Primary Bus number

• Bit 3: Secondary Bus number

• Bit 4: Secondary Bus number to Subordinate Bus number

window

• Bit 5: I/O window

• Bit 6: Non-Prefetchable window

• Bit 7: Prefetchable window

rx_st_data[<n>-1:0]

Output

Receive data bus. Note that the position of the first payload

dword depends on whether the TLP address is qword aligned.

The mapping of message TLPs is the same as the mapping of

TLPs with 4-dword headers.

rx_st_eop

Output

Indicates that this is the last cycle of the TLP when

rx_st_valid

is asserted.

rx_st_err

Output

Indicates that there is an ECC error in the internal RX buffer.

Active when ECC is enabled. ECC is automatically enabled by the

Quartus II assembler. ECC corrects single-bit errors and detects

double-bit errors on a per byte basis.

When an uncorrectable ECC error is detected,

rx_st_err

is

asserted for at least 1 cycle while

rx_st_valid

is asserted.

Altera recommends resetting the Arria V Hard IP for PCI

Express when an uncorrectable double-bit ECC error is detected.

UG-01105_avmm

2014.12.15

Hard IP Status Extension

4-17

Interfaces and Signal Descriptions

Altera Corporation