Featured device: stratix v gx fpga, I/o resources, Featured device: stratix v gx fpga –6 – Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 14: I/o resources –6

2–6

Chapter 2: Board Components

Featured Device: Stratix V GX FPGA

100G Development Kit, Stratix V GX Edition

August 2012

Altera Corporation

Reference Manual

Featured Device: Stratix V GX FPGA

The Stratix V GX 100G development board features the 5SGXEA7N2F45C2N Stratix V

GX FPGA device (U38) in a 1932-pin FBGA package.

f

For more information about the Stratix V GX devices, refer

describes the features of the Stratix V GX 5SGXEA7N2F45C2N device.

lists the Stratix V GX component reference and manufacturing information.

I/O Resources

summarizes the FPGA I/O usage by function on the Stratix V GX 100G

development board. The I/O direction is with respect to the FPGA.

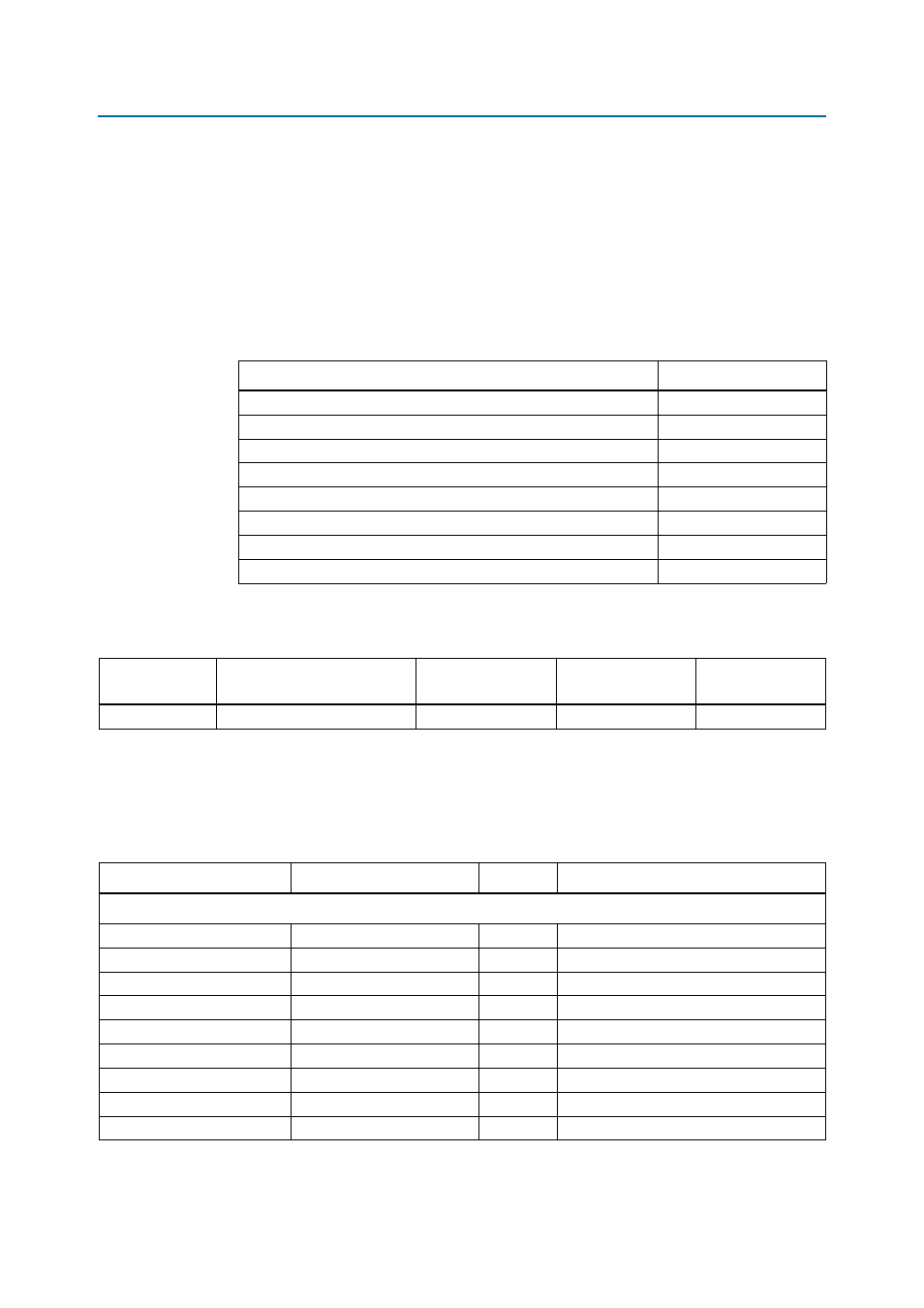

Table 2–2. Stratix V GX Device 5SGXEA7N2F45C2N Features

Features

Total

Equivalent LEs

622,000

M20K Memory Blocks (2048 × 72 bits)

2,560

M20K Memory (Mbits)

50

Total Transceiver Channels

48

18-bit × 18-bit Multipliers

512

27-bit × 27-bit Multipliers

256

PLLs

28

Maximum User I/O pins

840

Table 2–3. Stratix V GX Device Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U38

Stratix V GX F1932, Lead Free

Altera

Corporation

5SGXEA7N2F45C2N

Table 2–4. Stratix V GX I/O Usage Summary (Part 1 of 6)

Function

I/O Type

I/O Count

Description

FPGA Transceiver Clocks

REFCLK_CAP_QL0

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QL1

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QL2

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QL3

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QR0

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QR1

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QR2

2.5-V LVDS input

2

Differential REFCLK input

REFCLK_CAP_QR3

2.5-V LVDS input

2

Differential REFCLK input

REFCLKB_CAP_QL0

2.5-V LVDS input

2

Differential REFCLK input