Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 22

2–14

Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

100G Development Kit, Stratix V GX Edition

August 2012

Altera Corporation

Reference Manual

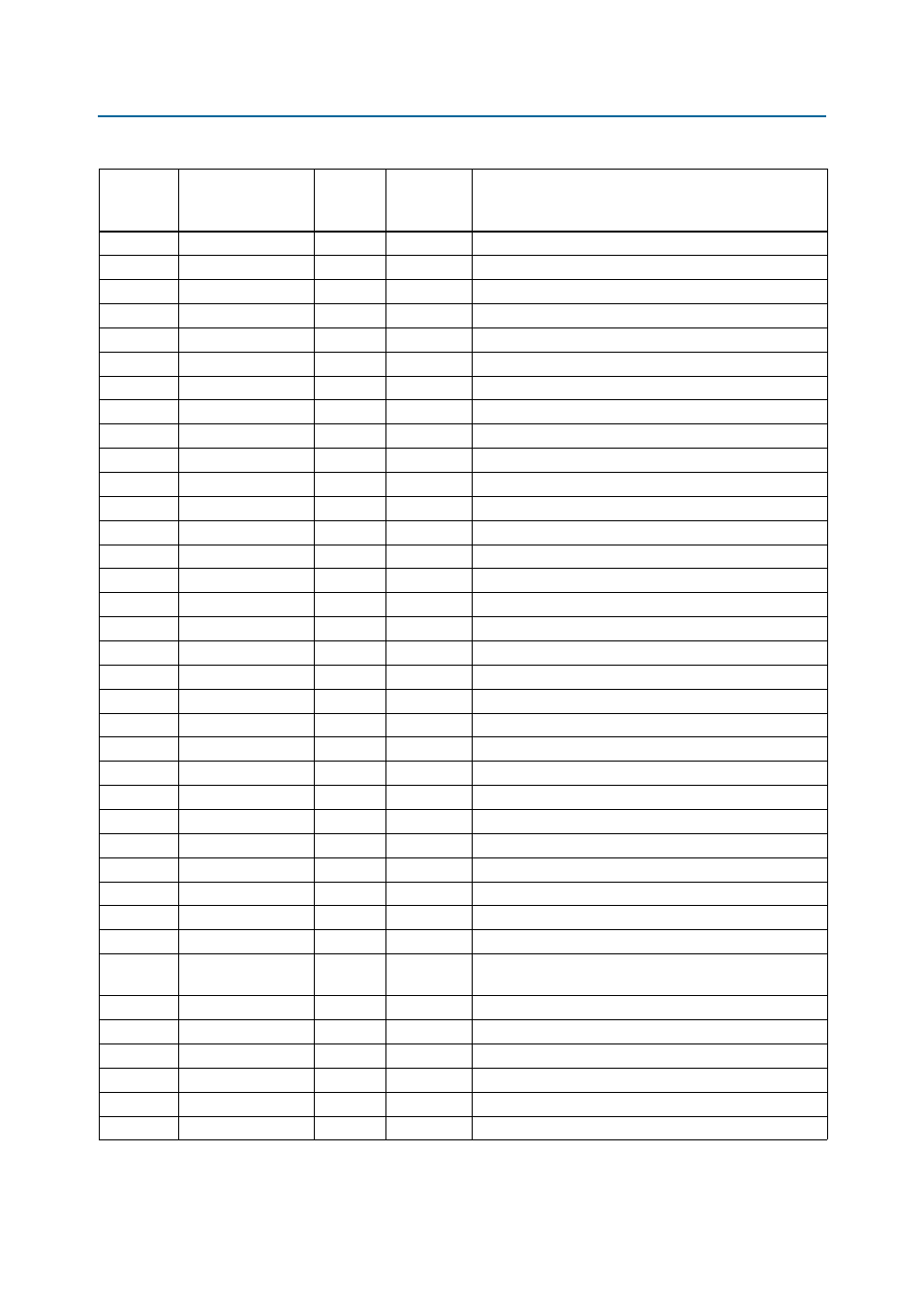

A5

FSM_A13

2.5-V

AE29

FSM bus flash address

B5

FSM_A14

2.5-V

AW22

FSM bus flash address

A4

FSM_A15

2.5-V

AN36

FSM bus flash address

A6

FSM_A16

2.5-V

AW9

FSM bus flash address

B3

FSM_A17

2.5-V

AT36

FSM bus flash address

B11

FSM_A18

2.5-V

BA21

FSM bus flash address

E8

FSM_A19

2.5-V

AJ12

FSM bus flash address

C8

FSM_A20

2.5-V

AD33

FSM bus flash address

C11

FSM_A21

2.5-V

AF34

FSM bus flash address

B8

FSM_A22

2.5-V

AH33

FSM bus flash address

C4

FSM_A23

2.5-V

AT20

FSM bus flash address

B4

FSM_A24

2.5-V

AJ33

FSM bus flash address

A2

FSM_A25

2.5-V

AW36

FSM bus flash address

B1

FSM_A26

2.5-V

BC20

FSM bus flash address

E10

FSM_D0

2.5-V

AG9

FSM bus flash data

A14

FSM_D1

2.5-V

AG11

FSM bus flash data

F10

FSM_D2

2.5-V

AY33

FSM bus flash data

F11

FSM_D3

2.5-V

BD35

FSM bus flash data

C5

FSM_D4

2.5-V

AV37

FSM bus flash data

D7

FSM_D5

2.5-V

AV35

FSM bus flash data

F7

FSM_D6

2.5-V

AL9

FSM bus flash data

C6

FSM_D7

2.5-V

AF13

FSM bus flash data

D11

FSM_D8

2.5-V

AP9

FSM bus flash data

B12

FSM_D9

2.5-V

AJ32

FSM bus flash data

F8

FSM_D10

2.5-V

AT33

FSM bus flash data

E7

FSM_D11

2.5-V

AK9

FSM bus flash data

D8

FSM_D12

2.5-V

AN38

FSM bus flash data

D5

FSM_D13

2.5-V

AJ21

FSM bus flash data

D6

FSM_D14

2.5-V

BC10

FSM bus flash data

E6

FSM_D15

2.5-V

BB36

FSM bus flash data

H13

INIT_DONE_LED

2.5-V

—

FPGA initialization done LED. Indicates that the FPGA is in

user mode.

N6

JTAG_MAX_TDO

2.5-V

—

MAX II CPLD on-board JTAG chain data out

P5

MAX_JTAG_TMS

2.5-V

—

MAX II CPLD on-board JTAG chain mode

H1

LCD_CSN

2.5-V

BA22

LCD display chip select

G7

LCD_D_CN

2.5-V

AR12

LCD data or control signal

G6

LCD_DATA0

2.5-V

BB39

LCD data

H2

LCD_DATA1

2.5-V

AR21

LCD data

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 5)

Board

Reference

(U59)

Schematic Signal

Name

I/O

Standard

Stratix V GX

Device Pin

Number

Pin Description