Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 17

Chapter 2: Board Components

2–9

Featured Device: Stratix V GX FPGA

August 2012

Altera Corporation

100G Development Kit, Stratix V GX Edition

Reference Manual

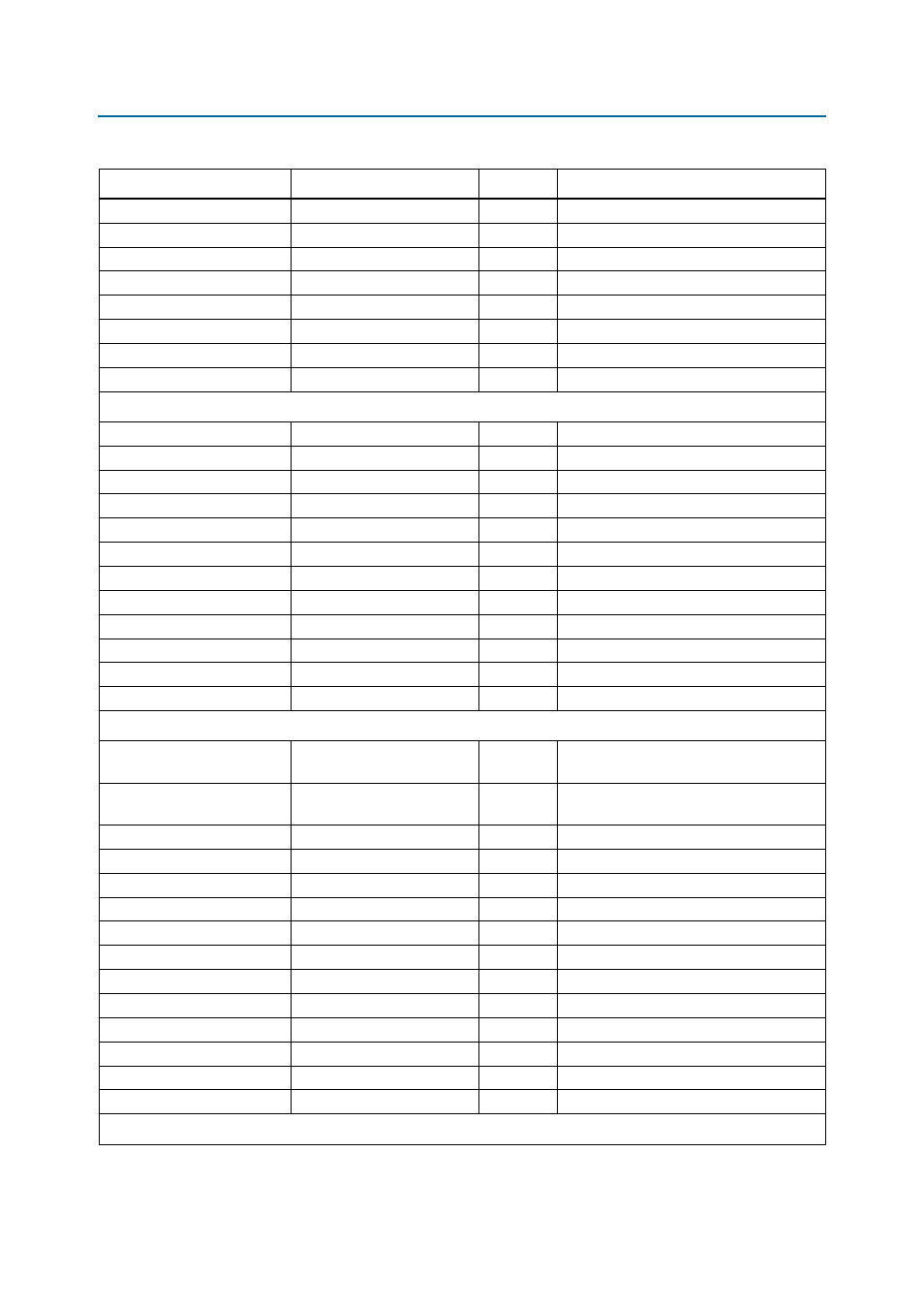

SFP_TXDISABLE

2.5-V LVCMOS output

1

SFP+ transmitter disable

SFP_RATESEL

2.5-V LVCMOS output

1

SFP+ rate select

SFP_MOD_PRSNTN

2.5-V LVCMOS input

1

SFP+ module present

SFP_MOD_ABS

2.5-V CMOS input

2

SFP+ module absent

SFP_SCL

2.5-V LVCMOS output

1

SFP+ serial two-wire clock

SFP_SDA

2.5-V LVCMOS bidirectional

1

SFP+ serial two-wire data

SFP_TXFAULT

2.5-V LVCMOS input

1

SFP+ transmitter fault

SFP_LOS

2.5-V LVCMOS input

1

SFP+ loss of signal

CFP

CFP_RX_P/_N[9:0]

Transceiver input

20

CFP receive channel

CFP_TX_P/_N[9:0]

Transceiver output

20

CFP transmit channel

CFP_PRG_CNTL[3:1]

2.5-V LVCMOS output

3

CFP programmable control I/O

CFP_MDC

2.5-V LVCMOS output

1

CFP management data I/O clock

CFP_MDIO

2.5-V LVCMOS bidirectional

1

CFP management data I/O data

CFP_MOD_RST

2.5-V LVCMOS output

1

CFP module reset

CFP_TX_DIS

2.5-V LVCMOS output

1

CFP transmitter disable

CFP_RX_LOS

2.5-V LVCMOS input

1

CFP loss of signal

CFP_PRG_ALRM[3:1]

2.5-V LVCMOS input

3

CFP programmable alarm

CFP_GLB_ALRM

2.5-V LVCMOS input

1

CFP global alarm

CFP_MOD_LOPWR

2.5-V LVCMOS output

1

CFP low power mode

CFP_MOD_ABS

2.5-V LVCMOS input

1

CFP module absent

Interlaken

INT_CAP_RX_P/_N[23:0]

Transceiver

non-inverted/inverted input

48

Interlaken receive channel

INT_TX_P/_N[23:0]

Transceiver

non-inverted/inverted output

48

Interlaken transmit channel

INT_LSB_CON_RX_FC_CK

2.5-V LVCMOS input

1

Interlaken reference clock input (LSB)

INT_LSB_CON_RX_FC_DATA

2.5-V LVCMOS input

1

Interlaken reference clock data (LSB)

INT_LSB_CON_RX_FC_SYNC

2.5-V LVCMOS input

1

Interlaken reference clock sync (LSB)

INT_LSB_CON_TX_FC_CK

2.5-V LVCMOS output

1

Interlaken reference clock output (LSB)

INT_LSB_CON_TX_FC_DATA

2.5-V LVCMOS output

1

Interlaken reference clock data (LSB)

INT_LSB_CON_TX_FC_SYNC

2.5-V LVCMOS output

1

Interlaken reference clock sync (LSB)

INT_MSB_CON_RX_FC_CK

2.5-V LVCMOS input

1

Interlaken reference clock input (MSB)

INT_MSB_CON_RX_FC_DATA

2.5-V LVCMOS input

1

Interlaken reference clock data (MSB)

INT_MSB_CON_RX_FC_SYNC

2.5-V LVCMOS input

1

Interlaken reference clock sync (MSB)

INT_MSB_CON_TX_FC_CK

2.5-V LVCMOS output

1

Interlaken reference clock output (MSB)

INT_MSB_CON_TX_FC_DATA

2.5-V LVCMOS output

1

Interlaken reference clock data (MSB)

INT_MSB_CON_TX_FC_SYNC

2.5-V LVCMOS output

1

Interlaken reference clock sync (MSB)

MAX II Bridge Control

Table 2–4. Stratix V GX I/O Usage Summary (Part 4 of 6)

Function

I/O Type

I/O Count

Description