Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 15

Chapter 2: Board Components

2–7

Featured Device: Stratix V GX FPGA

August 2012

Altera Corporation

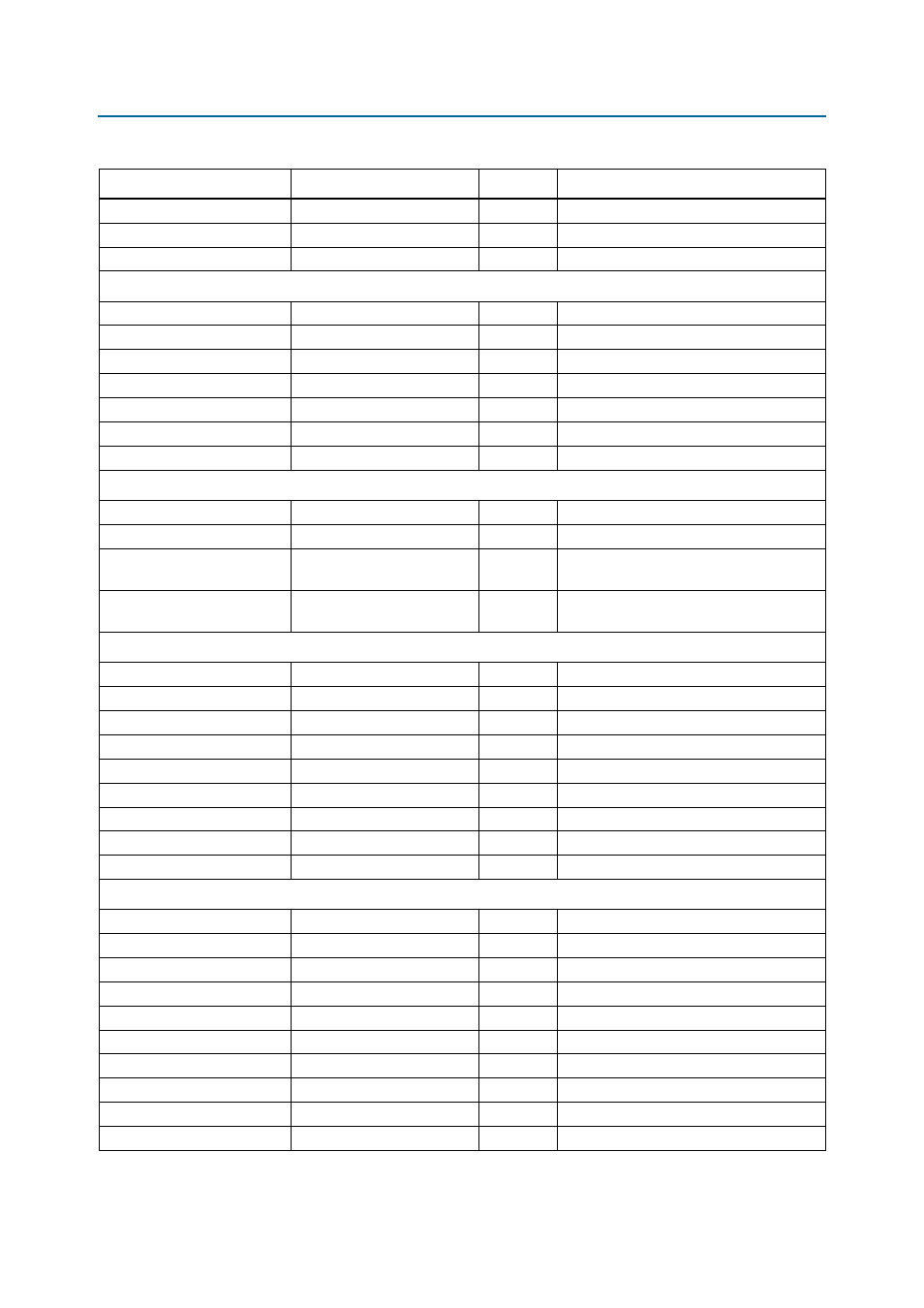

100G Development Kit, Stratix V GX Edition

Reference Manual

REFCLKB_CAP_QL2

2.5-V LVDS input

2

Differential REFCLK input

PRGCLK_QL1

2.5-V LVDS input

2

Differential REFCLK input

SMA_REFCLK_CAP

2.5-V LVDS input

2

Differential REFCLK input

FPGA Global Clocks

CLKIN_125

2.5-V LVDS input

2

Global clock

CLKIN_50_FPGA

2.5-V LVCMOS input

1

Global clock

DDR3A_CLK_IN

2.5-V LVDS input

2

Differential global clock

DIFFCLK_IN1

2.5-V LVDS input

2

Differential global clock

QDR2A_CLK_IN

2.5-V LVDS input

2

Differential global clock

QDR2B_CLK_IN

2.5-V LVDS input

2

Differential global clock

VCXOB_CLK_IN

2.5-V LVDS input

2

Differential global clock

SMA Transceivers

SMA_IN

2.5-V LVCMOS input

1

SMA clock input

SMA_OUT

2.5-V LVCMOS output

1

SMA clock output

SMA_RX_P/_N[1:0]

Transceiver

non-inverted/inverted input

4

SMA receive channel

SMA_TX_P/_N[1:0]

Transceiver

non-inverted/inverted output

4

SMA transmit channel

Flash

FLASH_ADVN

2.5-V LVCMOS output

1

Flash advance input

FLASH_CEN

2.5-V LVCMOS output

1

Flash chip enable

FLASH_CLK

2.5-V LVCMOS output

1

Flash clock

FLASH_OEN

2.5-V LVCMOS output

1

Flash output enable

FLASH_RDYBSYN

2.5-V LVCMOS output

1

Flash ready

FLASH_RESETN

2.5-V LVCMOS output

1

Flash reset

FLASH_WEN

2.5-V LVCMOS output

1

Flash write enable

FSM_A[25:1]

2.5-V LVCMOS output

25

Flash address bus

FSM_D[15:0]

2.5-V LVCMOS bidirectional

16

Flash data bus

DDR3 SDRAM (Six each)

DDR3_RZQIN

1.5-V

1

DDR3

DDR3_A[13:0]

1.5-V SSTL output

14

DDR3 address

DDR3_BA[2:0]

1.5-V SSTL output

3

DDR3 bank address

DDR3_DQS_P/_N[3:0]

Diff 1.5-V SSTL input

4

DDR3 data strobe

DDR3_DQ[31:0]

1.5-V SSTL bidirectional

32

DDR3 data

DDR3_CKE

1.5-V SSTL output

1

DDR3 clock enable

DDR3_CK_P/_N

Diff 1.5-V SSTL input

2

DDR3 clock

DDR3_CASN

1.5-V SSTL output

1

DDR3 chip select

DDR3_WEN

1.5-V SSTL output

1

DDR3 write enable

DDR3_RASN

1.5-V SSTL output

1

DDR3 RAS#

Table 2–4. Stratix V GX I/O Usage Summary (Part 2 of 6)

Function

I/O Type

I/O Count

Description