Qsfp interface, Qsfp interface –33 – Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 41

Chapter 2: Board Components

2–33

Components and Interfaces

August 2012

Altera Corporation

100G Development Kit, Stratix V GX Edition

Reference Manual

QSFP Interface

The development board includes two QSFP interfaces for a 40G QSFP module. The

QSFP interface can support four full-duplex transceiver channels.

lists the pin assignments for the first QSFP interface (J33) and their

corresponding schematic signal names and Stratix V GX pin numbers.

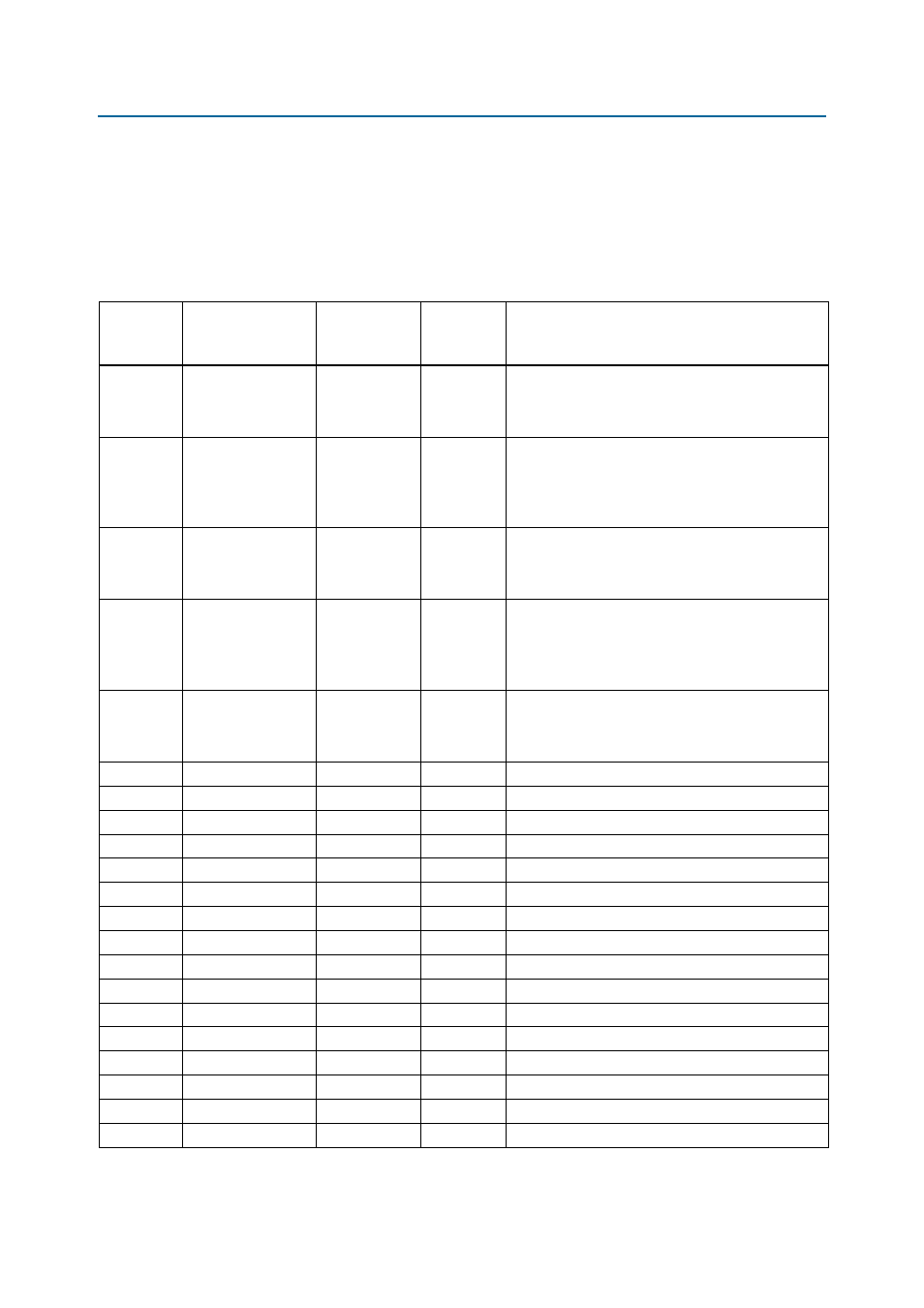

Table 2–26. QSFP Interface Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 2)

Board

Reference

(J33)

Schematic Signal

Name

I/O Standard

Stratix V GX

Device Pin

Number

Description

28

QSFP0_INTERRUPTN

2.5-V LVCMOS

AM22

Module interrupt output:

0: Possible module operational fault

1: Normal mode

31

QSFP0_LP_MODE

2.5-V LVCMOS

BC22

Low power mode input:

0: Set module for high-power mode

1: Set module for low-power mode (maximum power

consumption is 1.5 W)

27

QSFP0_MOD_PRSN

2.5-V LVCMOS

AR31

Module present (output):

0: Module present (inserted)

1: Module absent

8

QSFP0_MOD_SELN

2.5-V LVCMOS

AK20

Module select input:

0: Select module for two-wire serial communication

1: Module not available for two-wire serial

communication

9

QSFP0_RST

2.5-V LVCMOS

BC35

Module reset input:

0: Reset module

1: Normal mode

17

QSFP0_RX_P0

1.5-V PCML

AW4

Receive XCVR pair 0 from FPGA

18

QSFP0_RX_N0

1.5-V PCML

AW3

Receive XCVR pair 0 from FPGA

22

QSFP0_RX_P1

1.5-V PCML

AY2

Receive XCVR pair 1 from FPGA

21

QSFP0_RX_N1

1.5-V PCML

AY1

Receive XCVR pair 1 from FPGA

14

QSFP0_RX_P2

1.5-V PCML

AV2

Receive XCVR pair 2 from FPGA

15

QSFP0_RX_N2

1.5-V PCML

AV1

Receive XCVR pair 2 from FPGA

25

QSFP0_RX_P3

1.5-V PCML

AT2

Receive XCVR pair 3 from FPGA

24

QSFP0_RX_N3

1.5-V PCML

AT1

Receive XCVR pair 3 from FPGA

11

QSFP0_SCL

2.5-V LVCMOS

AU8

Two-wire serial clock input

12

QSFP0_SDA

2.5-V LVCMOS

AK35

Two-wire serial data

36

QSFP0_TX_P0

1.5-V PCML

AT6

Transmit XCVR pair 0 from FPGA

37

QSFP0_TX_N0

1.5-V PCML

AT5

Transmit XCVR pair 0 from FPGA

3

QSFP0_TX_P1

1.5-V PCML

AU4

Transmit XCVR pair 1 from FPGA

2

QSFP0_TX_N1

1.5-V PCML

AU3

Transmit XCVR pair 1 from FPGA

33

QSFP0_TX_P2

1.5-V PCML

AR4

Transmit XCVR pair 2 from FPGA

34

QSFP0_TX_N2

1.5-V PCML

AR3

Transmit XCVR pair 2 from FPGA