Altera 100G Development Kit, Stratix V GX Edition User Manual

Page 16

2–8

Chapter 2: Board Components

Featured Device: Stratix V GX FPGA

100G Development Kit, Stratix V GX Edition

August 2012

Altera Corporation

Reference Manual

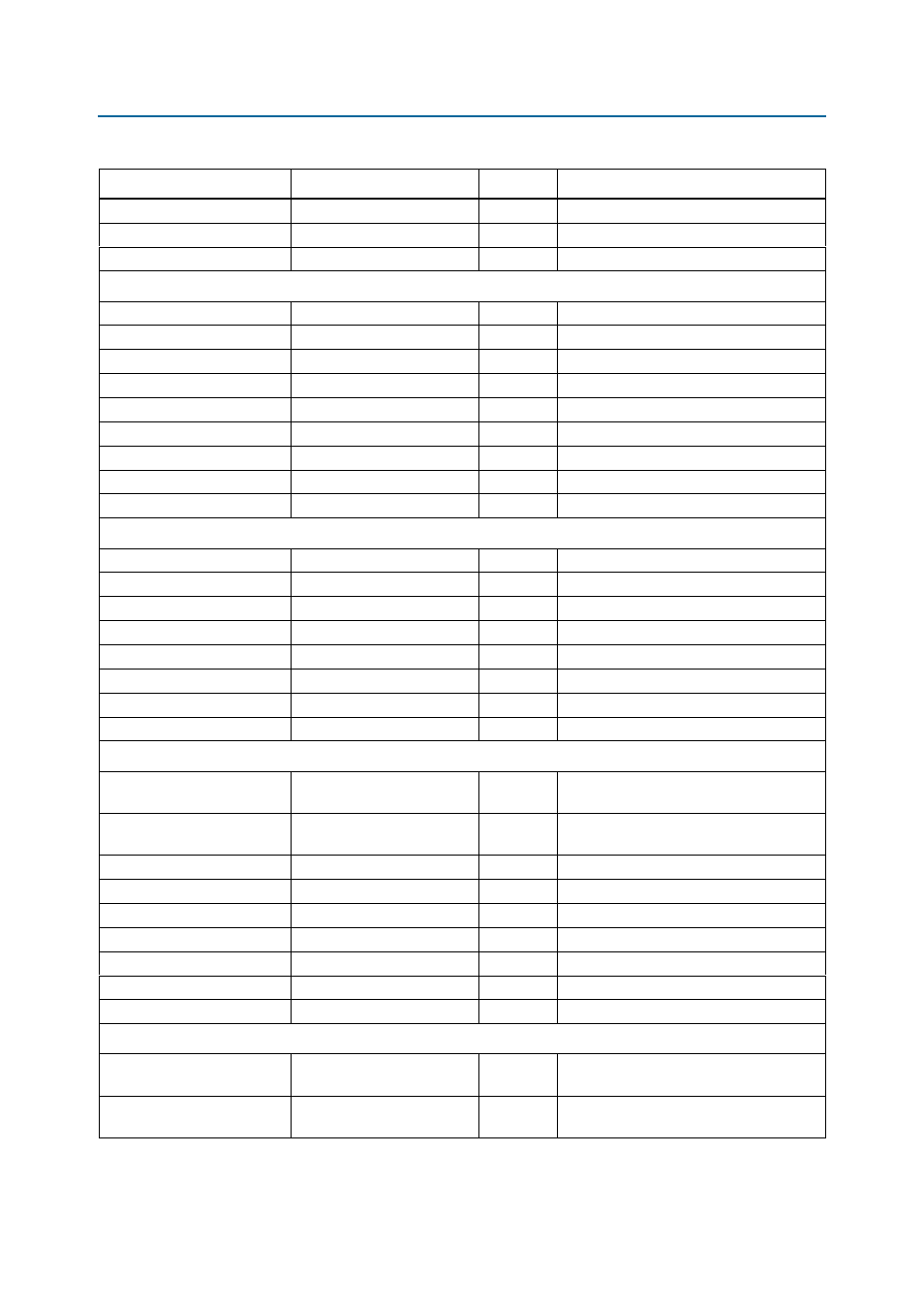

DDR3_CASN

1.5-V SSTL output

1

DDR3 CAS#

DDR3_RSTN

1.5-V SSTL output

1

DDR3 reset

DDR3_ODT

1.5-V SSTL output

1

DDR3 on-die termination

QDR II SRAM (x36)

QDR2A_RZQIN

1.5-V

1

QDR II

QDR2A_A[19:0]

1.5-V HSTL output

20

QDR II address

QDR2A_Q[35:0]

1.5-V HSTL input

36

QDR II data output

QDR2A_D[35:0]

1.5-V HSTL output

36

QDR II data input

QDR2A_BWSN[3:0]

1.5-V HSTL output

4

QDR II byte write select

QDR2A_WPSN

1.5-V HSTL output

1

QDR II write port select

QDR2A_RPSN

1.5-V HSTL output

1

QDR II read port select

QDR2A_K_P/_N

1.5-V HSTL output

2

QDR II clock input

QDR2A_CQ_P/_N

1.5-V HSTL output

2

QDR II echo clock

QDR II SRAM (x18)

QDR2B_A[20:0]

1.5-V HSTL output

21

QDR II address

QDR2B_Q[17:0]

1.5-V HSTL input

18

QDR II data output

QDR2B_D[17:0]

1.5-V HSTL output

18

QDR II data input

QDR2B_BWSN[1:0]

1.5-V HSTL output

2

QDR II byte write select

QDR2B_WPSN

1.5-V HSTL output

1

QDR II write port select

QDR2B_RPSN

1.5-V HSTL output

1

QDR II read port select

QDR2B_K_P/_N

1.5-V HSTL output

2

QDR II clock input

QDR2B_CQ_P/_N

1.5-V HSTL output

2

QDR II echo clock

QSFP (Two each)

QSFP_RX_P/_N[3:0]

Transceiver

non-inverted/inverted input

4

QSFP receive channel

QSFP_TX_P/_N[3:0]

Transceiver

non-inverted/inverted output

4

QSFP transmit channel

QSFP_MOD_SELN

2.5-V LVCMOS output

1

QSFP module select

QSFP_RST

2.5-V LVCMOS output

1

QSFP reset

QSFP_SCL

2.5-V LVCMOS output

1

QSFP serial two-wire clock

QSFP_SDA

2.5-V LVCMOS bidirectional

1

QSFP serial two-wire data

QSFP_INTERRUPTN

2.5-V LVCMOS output

1

QSFP interrupt

QSFP_MOD_PRSN

2.5-V LVCMOS input

1

QSFP module present

QSFP_LP_MODE

2.5-V LVCMOS output

1

QSFP low power mode

SFP+ (Four each)

SFP_RD_P/_N

Transceiver

non-inverted/inverted input

2

SFP+ receive channel

SFP_TD_P/_N

Transceiver

non-inverted/inverted output

2

SFP+ transmit channel

Table 2–4. Stratix V GX I/O Usage Summary (Part 3 of 6)

Function

I/O Type

I/O Count

Description