Test access module configuration menu, Test access module configuration menu -2, Figure – Verilink AS4000 (34-00244) Product Manual User Manual

Page 124

Test Access Module (TAM)

8-2

Verilink AS4000 User Manual

Test Access

Module

Configuration

Menu

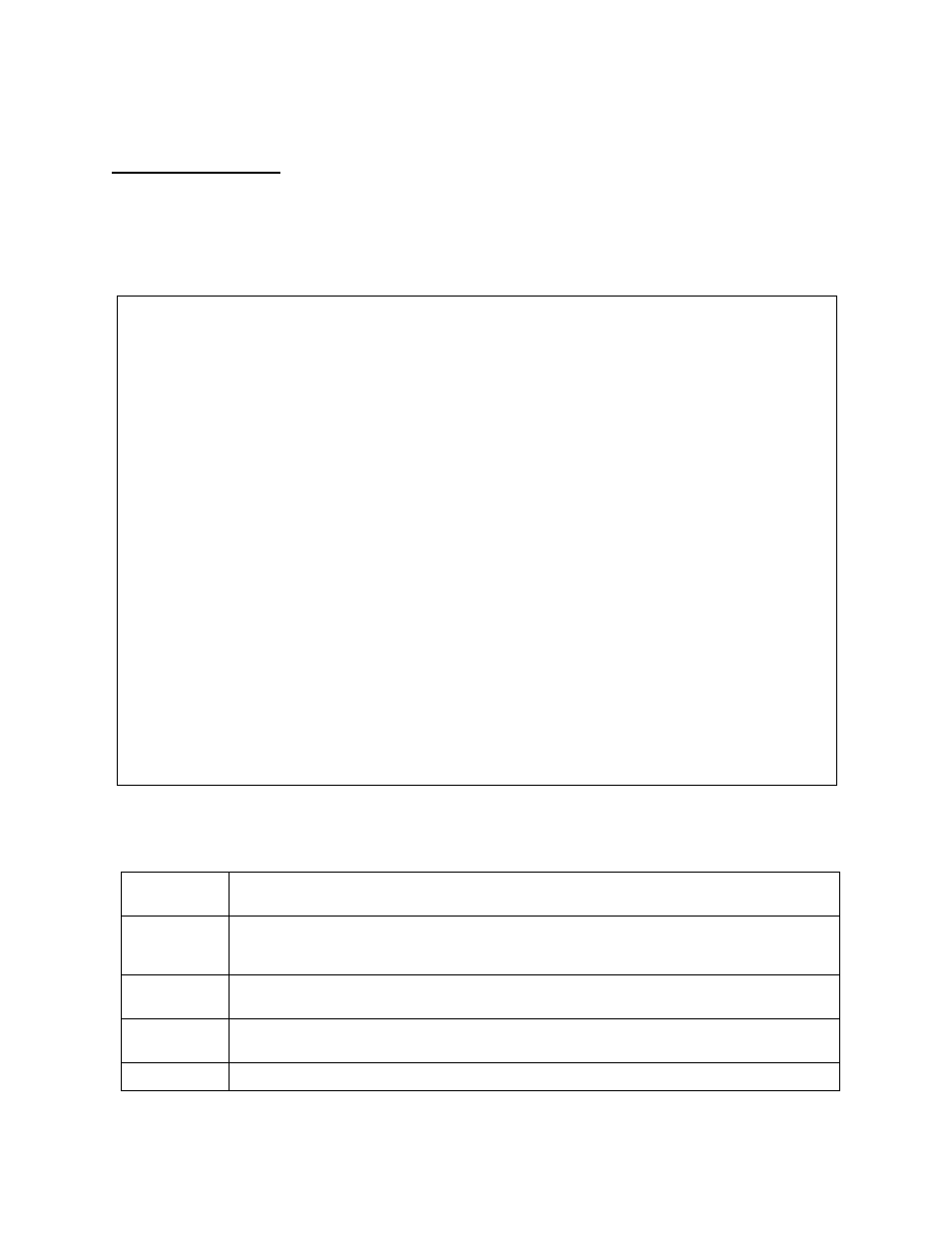

Use this menu to configure control leads, select electrical interface

types, and set the phase relationship of transmit data and transmit

clock.

Figure 8-2 Configuration Menu

The options on the TAM Configuration Menu are described in

.

Table 8-1

TAM Configuration Menu

Ve

Ve

Ve

Ver

r

r

rilink

ilink

ilink

ilink C

C

C

Corpor

orpor

orpor

orpora

a

a

ation

tion

tion

tion

AS40

AS40

AS40

AS4000 -

00 -

00 -

00 - T

T

T

Test A

est A

est A

est Ac

c

c

ccess

cess

cess

cess

Slot:

Slot:

Slot:

Slot:1

1

1

11

1

1

1 H

H

H

Help =

elp =

elp =

elp =

[?]

[?]

[?]

[?]

Co

Co

Co

Con

n

n

nfigur

figur

figur

figura

a

a

ation

tion

tion

tion m

m

m

menu

enu

enu

enu

Port

Port

Port

Port 1

1

1

1

Port 2

Port 2

Port 2

Port 2 Port

Port

Port

Port 3

3

3

3 Port

Port

Port

Port 4

4

4

4

Na

Na

Na

Nam

m

m

me.....

e.....

e.....

e.....:

:

:

: Test

Test

Test

Test One

One

One

One

Test

Test

Test

Test Two

Two

Two

Two

Test

Test

Test

Test Three

Three

Three

Three T

T

T

Test F

est F

est F

est Fo

o

o

our

ur

ur

ur

Sp

Sp

Sp

Spe

e

e

eed....

ed....

ed....

ed....:

:

:

: 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Ti

Ti

Ti

Tim

m

m

ming...

ing...

ing...

ing...:

:

:

: Inte

Inte

Inte

Inter

r

r

rnal

nal

nal

nal

Inte

Inte

Inte

Inter

r

r

rnal

nal

nal

nal

Inte

Inte

Inte

Inter

r

r

rnal

nal

nal

nal I

I

I

Intern

ntern

ntern

nterna

a

a

al

l

l

l

DC

DC

DC

DCD

D

D

D out..

out..

out..

out..:

:

:

: Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On

Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On

Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On F

F

F

Forced

orced

orced

orced On

On

On

On

DS

DS

DS

DSR

R

R

R out..

out..

out..

out..:

:

:

: Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On

Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On

Forc

Forc

Forc

Force

e

e

ed On

d On

d On

d On F

F

F

Forced

orced

orced

orced On

On

On

On

Da

Da

Da

Dat

t

t

ta.....

a.....

a.....

a.....:

:

:

: Norm

Norm

Norm

Norma

a

a

al

l

l

l

Norm

Norm

Norm

Norma

a

a

al

l

l

l

Norm

Norm

Norm

Norma

a

a

al

l

l

l N

N

N

Normal

ormal

ormal

ormal

Cl

Cl

Cl

Clo

o

o

ock....

ck....

ck....

ck....:

:

:

: Norm

Norm

Norm

Norma

a

a

al

l

l

l

Norm

Norm

Norm

Norma

a

a

al

l

l

l

Norm

Norm

Norm

Norma

a

a

al

l

l

l N

N

N

Normal

ormal

ormal

ormal

In

In

In

Int

t

t

terface

erface

erface

erface:

:

:

: V.35

V.35

V.35

V.35

V.35

V.35

V.35

V.35

V.35

V.35

V.35

V.35 V

V

V

V.35

.35

.35

.35

V.

V.

V.

V.5

5

5

54 loop

4 loop

4 loop

4 loop:

:

:

: Disa

Disa

Disa

Disab

b

b

bled

led

led

led

Disa

Disa

Disa

Disab

b

b

bled

led

led

led

Disa

Disa

Disa

Disab

b

b

bled

led

led

led D

D

D

Disabl

isabl

isabl

isable

e

e

ed

d

d

d

Na

Na

Na

Nav

v

v

vigate

igate

igate

igate m

m

m

menu

enu

enu

enu

= [S

= [S

= [S

= [Sp

p

p

pace/B

ace/B

ace/B

ace/Ba

a

a

ackspa

ckspa

ckspa

ckspac

c

c

ce]

e]

e]

e]

Ch

Ch

Ch

Cha

a

a

ange pa

nge pa

nge pa

nge par

r

r

ramete

amete

amete

ameter

r

r

r = [R

= [R

= [R

= [Re

e

e

eturn/

turn/

turn/

turn/'

'

'

'B']

B']

B']

B']

Ex

Ex

Ex

Exi

i

i

it/abor

t/abor

t/abor

t/abort

t

t

t edit

edit

edit

edits

s

s

s = ['

= ['

= ['

= ['X

X

X

X'/Esc

'/Esc

'/Esc

'/Esc]

]

]

]

Name

This is a user-defined field. Any name up to 14 characters in length can be entered to

identify each port on the Test Access Module.

Speed

The Test Access Module operates at speeds from 48 kbit/s to 2.048 Mbit/s, and any

multiple of 56/64 kbit/s. Latching loopback sequences can be performed only at 56/64

kbit/s.

Timing

The tester interface timing is set to Internal and can not be changed. Test equipment

attached to the TAM I/O port must accept clocks from the TAM.

DCD Out

The TAM card presents a DCE interface to the attached test equipment. Carrier detect

can be Forced Off, Forced On, or Track RTS (DCD is On if RTS is On).

DSR Out

Data Set Ready can be Forced Off, Forced On, or Track DTR.