Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 16

2–8

Chapter 2: Board Components

Featured Device: Stratix IV GT Device

100G Development Kit, Stratix IV GT Edition Reference Manual

September 2010

Altera Corporation

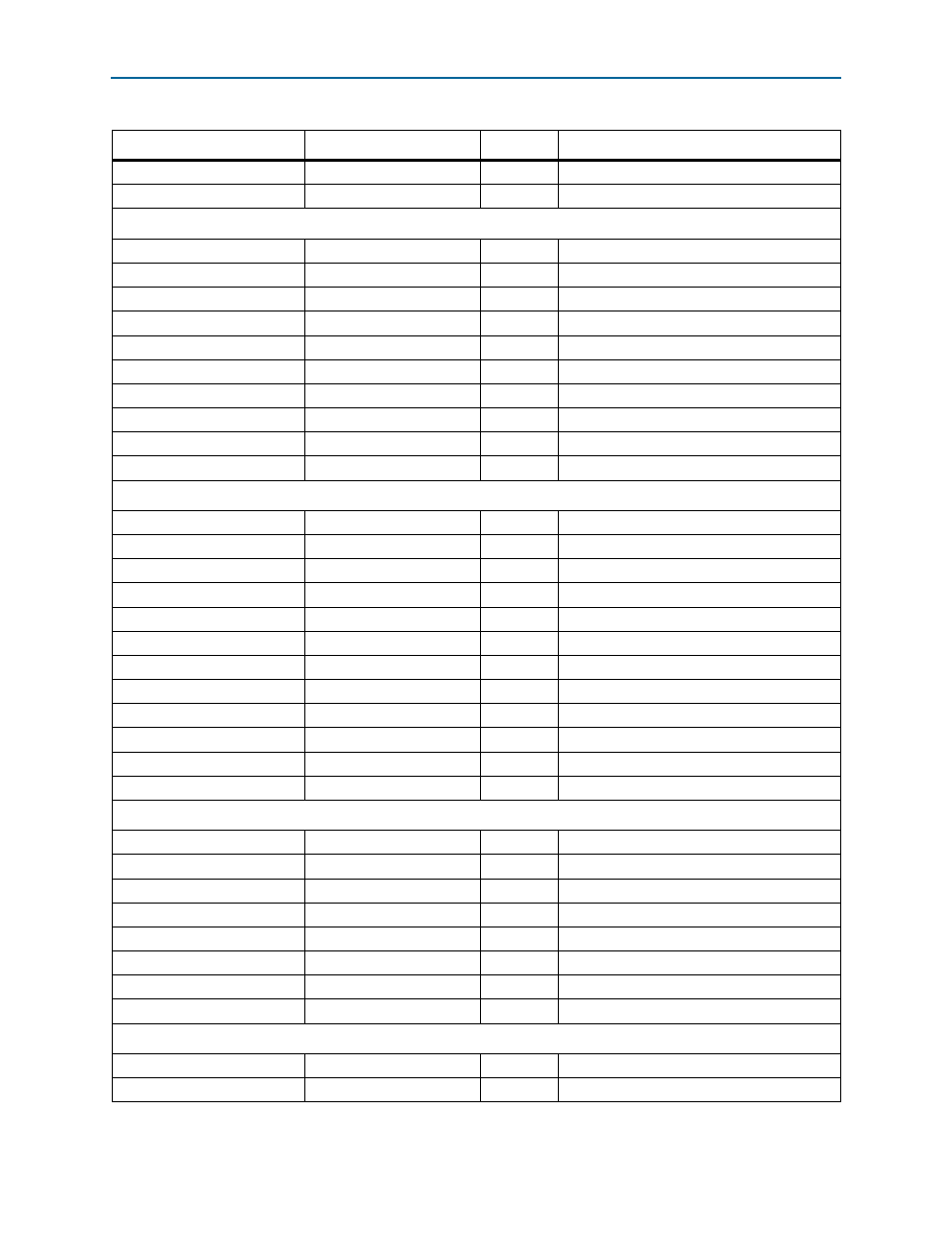

SMA diff clock input

LVDS input

2

Diff global clock

SMA diff I/O or clock output

—

2

Diff global I/O or clock output

Flash/SSRAM

ADDR[26:1]

2.5-V CMOS input

26

Flash address bus

DATA[31:0]

2.5-V CMOS input

32

Flash data bus

SSRAM_OEn

2.5-V CMOS output

1

SSRAM output enable

SSRAM_BWn[3:0]

2.5-V CMOS output

4

SSRAM byte write select

SSRAM_BWEn

2.5-V CMOS output

1

SSRAM byte write enable

SSRAM_ADVn

2.5-V CMOS output

1

SSRAM advance input

SSRAM_ADSCn

2.5-V CMOS output

1

SSRAM address strobe from controller

SSRAM_ADSPn

2.5-V CMOS output

1

SSRAM address strobe from processor

SSRAM_CE1n

2.5-V CMOS output

1

SSRAM chip enable

SSRAM_CLK

2.5-V CMOS output

1

SSRAM clock

DDR3 SDRAM (Four each)

DDR3_BA[2:0]

1.5-V SSTL output

12

DDR3 bank address

DDR3_DQS_P/_N[3:0]

Diff 1.5-V SSTL input

32

DDR3 data strobe

DDR3_ADDR[12:0]

1.5-V SSTL output

52

DDR3 address

DDR3_DQ[31:0]

1.5-V SSTL input

128

DDR3 data

DDR3_CKE

1.5-V SSTL output

4

DDR3 clock enable

DDR3_CK_P/_N

Diff 1.5-V SSTL input

8

DDR3 clock

DDR3_CSn

1.5-V SSTL output

4

DDR3 chip select

DDR3_Wen

1.5-V SSTL output

4

DDR3 write enable

DDR3_RASn

1.5-V SSTL output

4

DDR3 RAS#

DDR3_CASn

1.5-V SSTL output

4

DDR3 CAS#

DDR3_RSTn

1.5-V SSTL output

4

DDR3 reset

DDR3_ODT

1.5-V SSTL output

4

DDR3 on-die termination

QDR II SRAM (Four each)

QDR2_ADDR[20:0]

1.5-V SSTL output

84

QDR II address

QDR2_Q[17:0]

1.5-V SSTL input

72

QDR II data output

QDR2_D[17:0]

1.5-V SSTL output

72

QDR II data input

QDR2_BWSn[1:0]

1.5-V SSTL output

8

QDR II byte write select

QDR2_WPSn

1.5-V SSTL output

4

QDR II write port select

QDR2_RPSn

1.5-V SSTL output

4

QDR II read port select

QDR2_K_P/_N

Diff 1.5-V SSTL output

8

QDR II clock input

QDR2_CQ_P/_N

Diff 1.5-V SSTL input

8

QDR II echo clock

QSFP

QSFP_RX_P/_N[3:0]

Transceiver Channel

8

QSFP receive channel

QSFP_TX_P/_N[3:0]

Transceiver Channel

8

QSFP transmit channel

Table 2–4. Stratix IV GT I/O Usage Summary (Part 2 of 5)

Function

I/O Type

I/O Count

Description