Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 21

Chapter 2: Board Components

2–13

MAX II CPLD EPM2210 System Controller

September 2010

Altera Corporation

100G Development Kit, Stratix IV GT Edition Reference Manual

U72.J13

50-MHz clock input

Input

CLKIN_50_MAX

—

U67.5

U72.H17

FPGA initialization LED

Output

CONFIGN_LED

—

U40.2

U72.J1

Power monitor SPI clock

Output

CSENSE_SCK

—

U61.5

U72.H6

Power monitor SPI input data

Output

CSENSE_SDI

—

U61.4

U72.K1

Power monitor SPI output data

Input

CSENSE_SDO

—

U62.5

U72.M3

Loads factory image into the FPGA

Output

FACTORY

—

S12.2

U72.A9

FSM bus flash byte enable feature

Output

FLASH_BYTEN

—

U65.F7

U72.D9

FSM bus flash chip enable

Input

FLASH_CEN

—

U65.F2

U72.R14

Control signal from the FPGA to

indicate flash information being

passed through the MAX_STRATIX

interface.

Output

FLASH_CONTROL

U44.AR34

—

U72.E9

FSM bus flash output enable

Output

FLASH_OEN

—

U65.G2

U72.B9

FSM bus flash ready

Output

FLASH_RDYBSYN

—

U65.A4

U72.F9

FSM bus flash reset

Output

FLASH_RESETN

—

U65.B5

U72.A8

FSM bus flash write enable

Output

FLASH_WEN

—

U65.A5

U72.B15

FPGA configuration done

Input

FPGA_CONF_DONE

U44.AW38

TP7

U72.A15

Initiates new image to the FPGA

Output

FPGA_CONFIGN

U44.BA36

TP10

U72.B18

FPGA configuration data

Output

FPGA_DATA0

U44.AA33

TP13

U72.D14

FPGA configuration data

Output

FPGA_DATA1

U44.Y32

TP14

U72.A17

FPGA configuration data

Output

FPGA_DATA2

U44.P38

TP15

U72.E13

FPGA configuration data

Output

FPGA_DATA3

U44.P37

TP16

U72.B16

FPGA configuration data

Output

FPGA_DATA4

U44.U38

TP17

U72.D13

FPGA configuration data

Output

FPGA_DATA5

U44.U37

TP18

U72.C15

FPGA configuration data

Output

FPGA_DATA6

U44.R40

TP19

U72.F12

FPGA configuration data

Output

FPGA_DATA7

U44.P39

TP20

U72.C14

FPGA configuration clock

Output

FPGA_DCLK

U44.AY9

TP9

U72.E12

FPGA configuration error

Input

FPGA_STATUSN

U44.AY36

TP11

U72.E11

FSM bus flash address

Bidirectional

FSM_A1

U44.AR6

U65.E2

U72.B14

FSM bus flash address

Bidirectional

FSM_A2

U44.AL13

U65.E2, U57.R6

U72.B13

FSM bus flash address

Bidirectional

FSM_A3

U44.AV6

U65.C2, U57.P6

U72.A12

FSM bus flash address

Bidirectional

FSM_A4

U44.AN6

U65.A2, U57.A2

U72.A13

FSM bus flash address

Bidirectional

FSM_A5

U44.AA14

U65.B2, U57.A10

U72.C13

FSM bus flash address

Bidirectional

FSM_A6

U44.AN39

U65.D3, U57.B2

U72.C12

FSM bus flash address

Bidirectional

FSM_A7

U44.T6

U65.C3, U57.B10

U72.D10

FSM bus flash address

Bidirectional

FSM_A8

U44.P7

U65.A3, U57.P2

U72.A7

FSM bus flash address

Bidirectional

FSM_A9

U44.Y14

U65.B6, U57.N6

U72.B6

FSM bus flash address

Bidirectional

FSM_A10

U44.AA31

U65.A6, U57.P3

U72.B7

FSM bus flash address

Bidirectional

FSM_A11

U44.AJ7

U65.C6, U57.P4

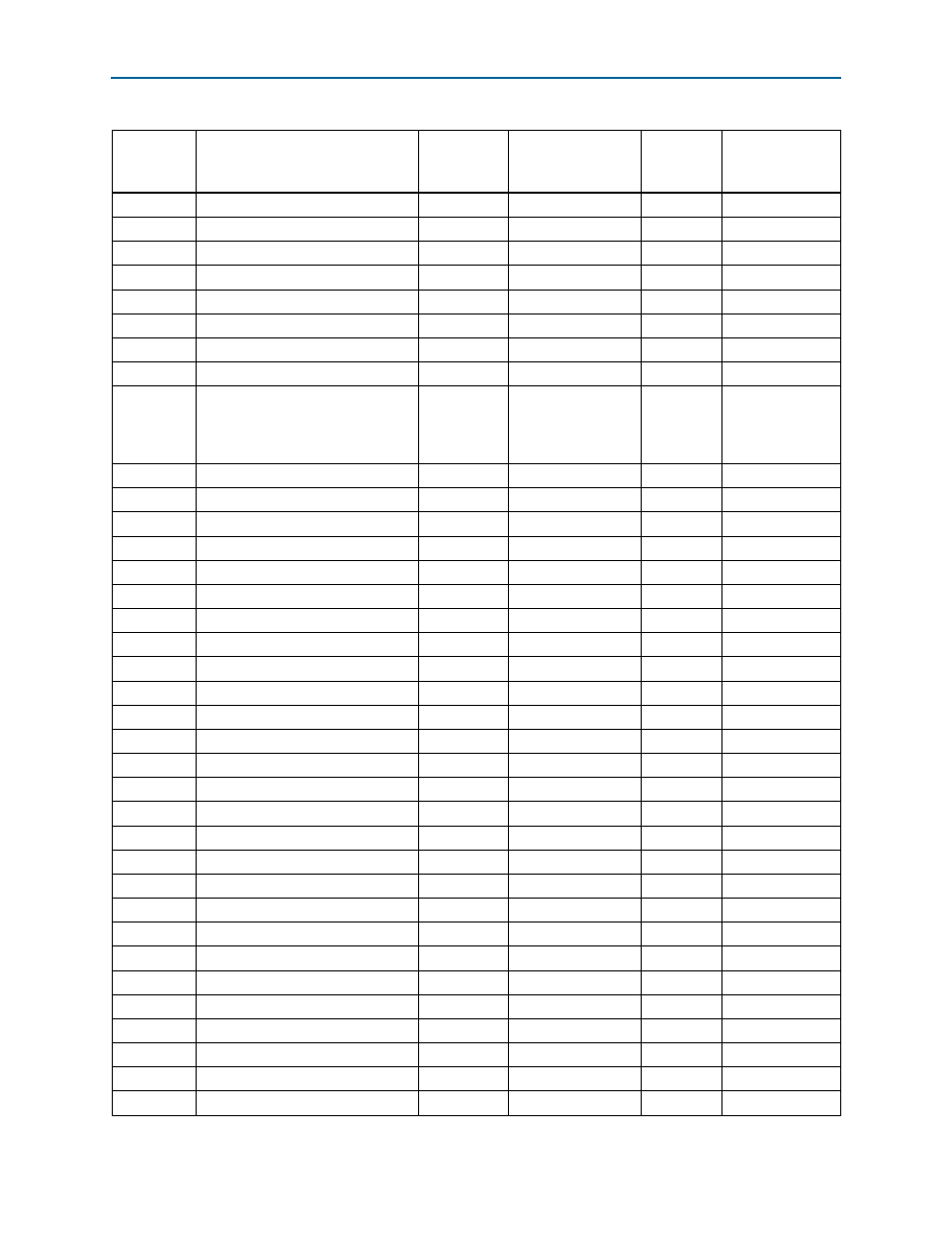

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 2 of 6)

EPM2210

Pin Number

Description

Type

Schematic Signal

Name

Stratix IV

GT Device

Pin Name

Other

Connections