External memory interfaces, External memory interfaces –48 – Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 56

2–48

Chapter 2: Board Components

Components and Interfaces

100G Development Kit, Stratix IV GT Edition Reference Manual

September 2010

Altera Corporation

lists the Interlaken interface component reference and manufacturing

information.

External Memory Interfaces

This section describes the board’s memory interface support, signal names, types, and

connectivity relative to the Stratix IV GT device.

The development board contains two types of external memory interfaces that utilizes

the top, bottom, and some sides of the Stratix IV GT device.

■

DDR3 Interface—eight 16-bit DDR3 devices that comprise of 4x32 independent

interfaces.

■

QDR II Interface—four 18-bit QDR II devices that comprise of 4x18 independent

interfaces.

J5.B1

Receive clock for the second 10 bits

of the bus

INT_MSB_CON_RX_CLK_N

1.2-V

PCML

—

J35.1

J5.A1

Receive clock for the second 10 bits

of the bus

INT_MSB_CON_RX_CLK_P

—

J33.1

J5.E10

Receive flow control clock signal for

the second 10 bits of the bus

INT_MSB_CON_RX_FC_CK

LVCMOS

AP39

—

J5.H7

Receive flow control data signal for

the second 10 bits of the bus

INT_MSB_CON_RX_FC_DATA

AN35

—

J5.H9

Receive flow control synchronization

signal for the second 10 bits of the

bus

INT_MSB_CON_RX_FC_SYNC

AM35

—

J30.B1

Transmit clock for the second 10 bits

of the bus

INT_MSB_CON_TX_CLK_N

1.2-V

PCML

E42

—

J30.A1

Transmit clock for the second 10 bits

of the bus

INT_MSB_CON_TX_CLK_P

E41

—

J30.E10

Transmit flow control clock signal for

the second 10 bits of the bus

INT_MSB_CON_TX_FC_CK

LVCMOS

L38

—

J30.H7

Transmit flow control data signal for

the second 10 bits of the bus

INT_MSB_CON_TX_FC_DATA

AN37

—

J30.H9

Transmit flow control

synchronization signal for the

second 10 bits of the bus

INT_MSB_CON_TX_FC_SYNC

AR39

—

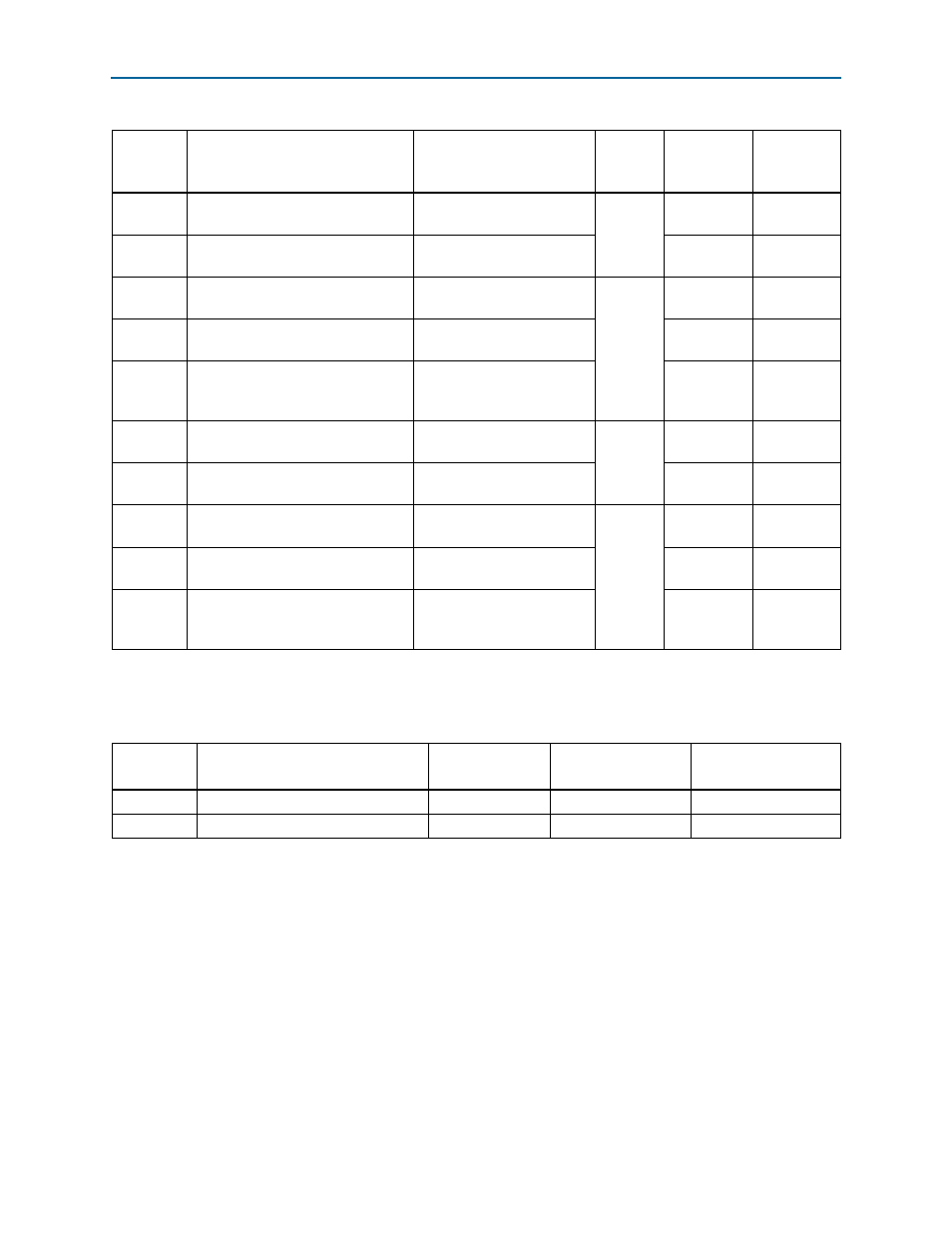

Table 2–35. Interlaken Interface Pin Assignments, Schematic Signal Names, and Functions (Part 4 of 4)

Board

Reference

Description

Schematic

Signal Name

i/O

Standard

Stratix IV GT

Device

Pin Name

Other

Connections

Table 2–36. Interlaken interface Component Reference And Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

J30, J57

Interlaken interface header

FCI

10035515-101LF

J5, J39

Interlaken interface receptical

FCI

10045722-101LF