Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 34

2–26

Chapter 2: Board Components

Clock Circuitry

100G Development Kit, Stratix IV GT Edition Reference Manual

September 2010

Altera Corporation

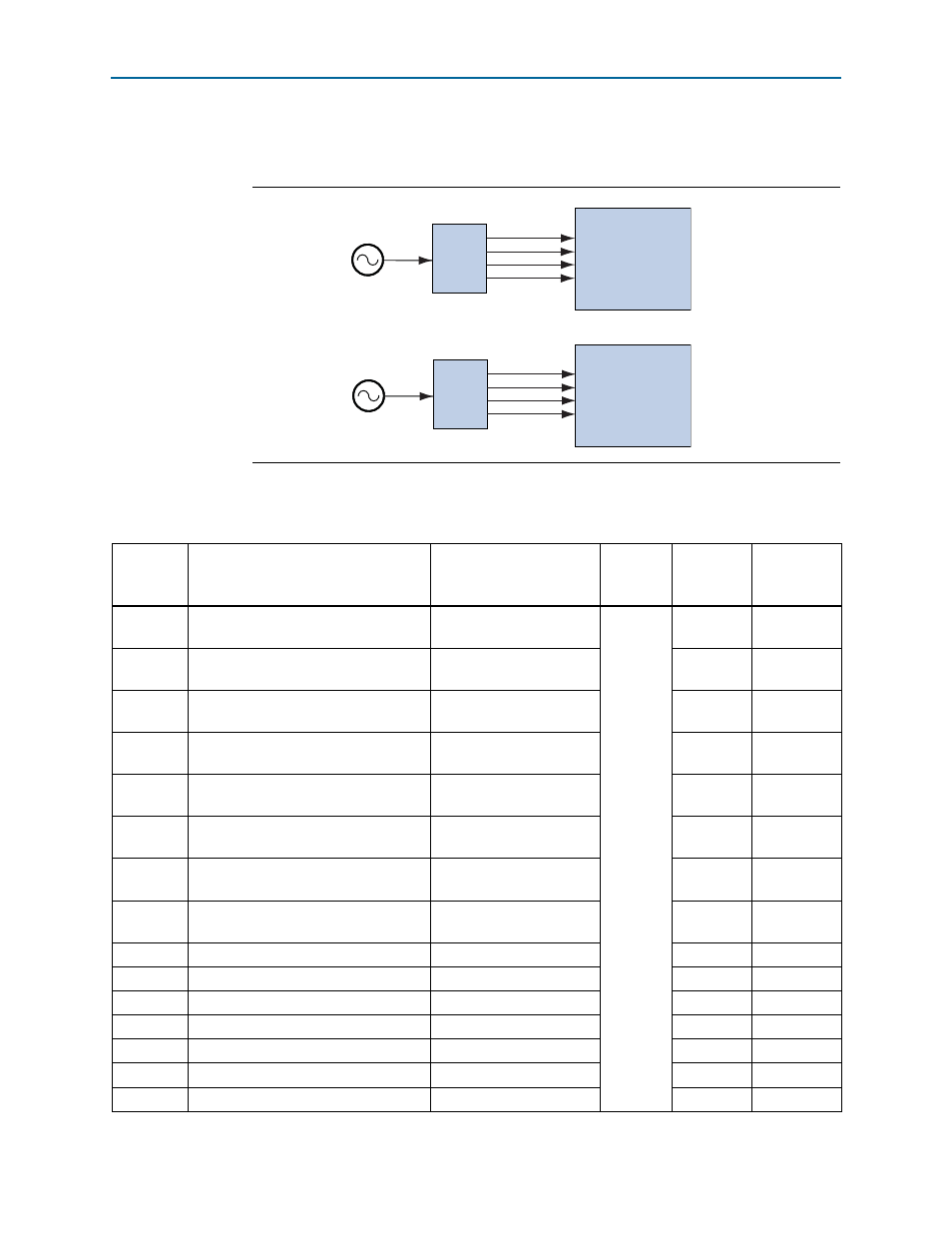

Two PLL/buffer devices (Si5338) drive the DDR3 and QDR II interfaces clocks

directly to the FPGA clock pins (as shown in the

).

Table 2–14

lists the clock signal names, board references, and functional descriptions.

Figure 2–9. Memory Clocks

PLL

25 MHz

Stratix IV GT

DDR3 Clocks

Si5338

PLL

25 MHz

QDR II Clocks

Si5338

Stratix IV GT

Table 2–14. Spread Spectrum Configuration DIP Switch Pin-Out (SW2) (Part 1 of 3)

Board

Reference

Description

Schematic

Signal Name

I/O

Standard

Stratix IV

GT Device

Pin Name

Other

Connections

U21.9

XCVR PLL clock for differential clock

buffer A

BUFFA1_DIFF_CLK_P

LVDS

—

U19.6

U21.10

XCVR PLL clock for differential clock

buffer A

BUFFA1_DIFF_CLK_N

—

U19.7

U21.13

XCVR PLL clock for reference clock

buffer A

BUFFA2_REF_CLK_P

—

U15.6

U21.14

XCVR PLL clock for reference clock

buffer A

BUFFA2_REF_CLK_N

—

U15.7

U21.17

XCVR PLL clock for differential clock

buffer B

BUFFB1_DIFF_CLK_P

—

U18.6

U21.18

XCVR PLL clock for differential clock

buffer B

BUFFB1_DIFF_CLK_N

—

U18.7

U21.21

XCVR PLL clock for reference clock

buffer B

BUFFB2_REF_CLK_P

—

U20.16

U21.22

XCVR PLL clock for reference clock

buffer B

BUFFB2_REF_CLK_N

—

U20.15

U22.9

DDR3 PLL clock A

DDR3_CLKA_P

J21

—

U22.10

DDR3 PLL clock A

DDR3_CLKA_N

J20

—

U22.13

DDR3 PLL clock B

DDR3_CLKB_P

N24

—

U22.14

DDR3 PLL clock B

DDR3_CLKB_N

N23

—

U22.17

DDR3 PLL clock C

DDR3_CLKC_P

M22

—

U22.18

DDR3 PLL clock C

DDR3_CLKC_N

M21

—

U22.21

DDR3 PLL clock D

DDR3_CLKD_P

R23

—