Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 18

2–10

Chapter 2: Board Components

Featured Device: Stratix IV GT Device

100G Development Kit, Stratix IV GT Edition Reference Manual

September 2010

Altera Corporation

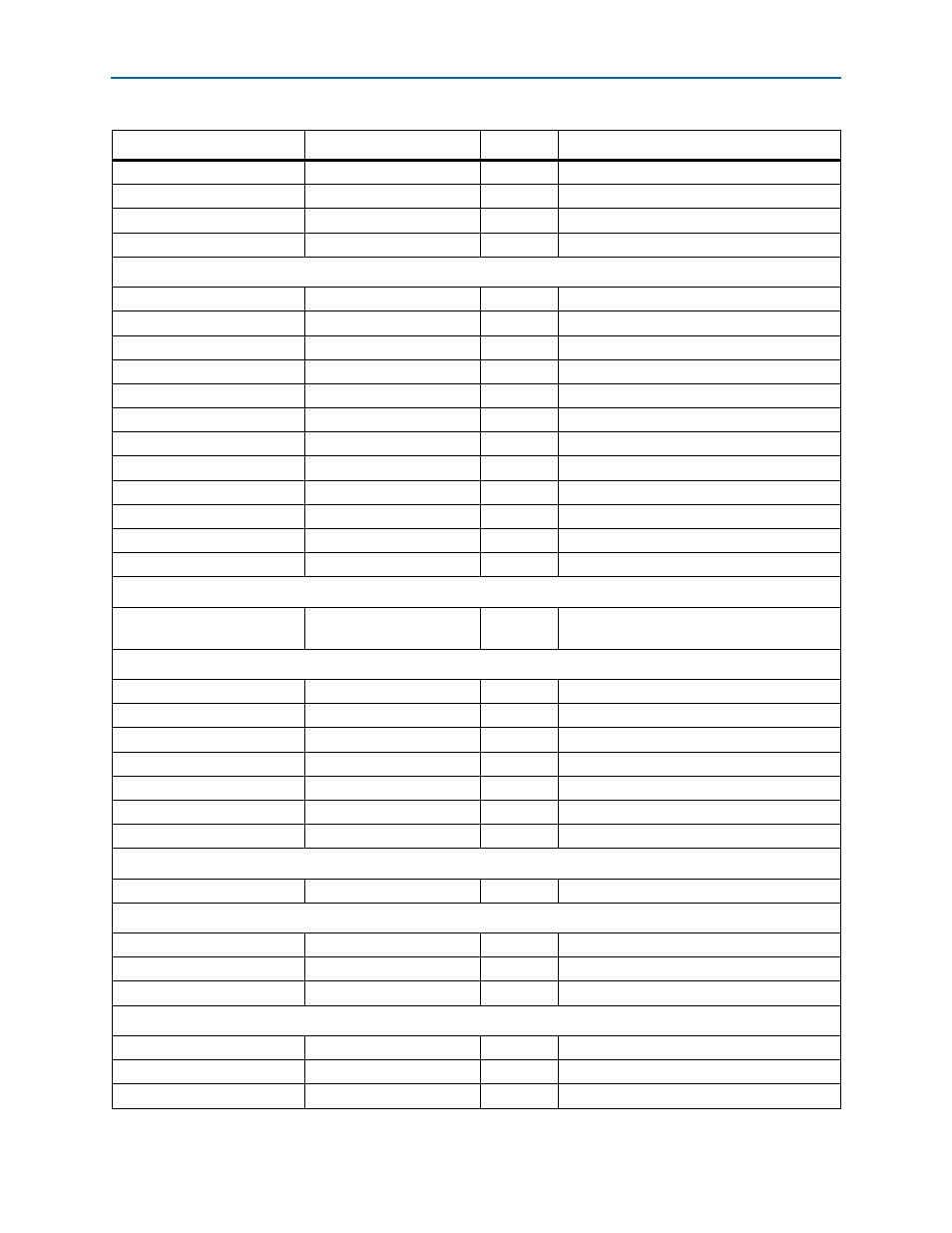

INT_TX_P/_N[19:0]

Transceiver channel

40

Interlaken transmit channel

INT_LSB_CON_TX_CLK_P/_N

1.2-V PCML

2

Interlaken reference clock input (LSB)

INT_MSB_CON_TX_CLK_P/_N

1.2-V PCML

2

Interlaken reference clock input (MSB)

INT_FLOW_CONTROL Signals

2.5-V CMOS

12

Interlaken flow control

MAX_STRATIX Bridge

FLASH_CONTROL

2.5-V CMOS output

1

FPGA flash control

MS_FLASH_BYTEN

2.5-V CMOS output

1

FPGA LCD write enable

MAX_STRATIX_RW

2.5-V CMOS output

1

FPGA Flash write enable

MAX_STRATIX_RDY

2.5-V CMOS output

1

FPGA Flash output enable

MAX_STRATIX_A[0]

2.5-V CMOS output

1

MAX output enable

MAX_STRATIX_A[1]

2.5-V CMOS output

1

MAX write enable

MAX_STRATIX_A[2]

2.5-V CMOS output

1

MAX chip select

MAX_STRATIX_A[3]

2.5-V CMOS output

1

FPGA LCD chip select

MAX_STRATIX_D[0]

2.5-V CMOS output

1

FPGA flash reset

MAX_STRATIX_D[1]

2.5-V CMOS output

1

MAX_STRATIX_D[1]

MAX_STRATIX_D[2]

2.5-V CMOS output

1

MAX_STRATIX_D[2]

MAX_STRATIX_D[3]

2.5-V CMOS output

1

MAX_STRATIX_D[3]

USB-Blaster

JTAG USB-Blaster or JTAG

header

2.5-V CMOS

5

Built-in USB-Blaster or JTAG 0.1-inch header

for debug purposes.

FPP Configuration

FPGA DCLK

2.5-V CMOS input

1

FPP Dclk

FPGA D[7:0]

2.5-V CMOS input

8

FPP data

MSEL [2:0]

2.5-V CMOS input

3

Dedicated configuration pins

NCONFIG

2.5-V CMOS input

1

Dedicated configuration pins

NSTATUS

2.5-V CMOS inout

1

Dedicated configuration pins

NCE

2.5-V CMOS input

1

Dedicated configuration pins

CONFIG_DONE

2.5-V CMOS inout

1

Dedicated configuration pins

Resets

CPU_RESETn

2.5-V CMOS input

1

Nios

®

II CPU Reset

Switches, Buttons, LEDS

User Push-buttons

2.5-V CMOS input

6

6 User Push-buttons

User DIP Switches

2.5-V CMOS input

8

8 User DIP Switches

User LEDS

2.5-V CMOS output

8

8 User LEDs (Green)

Ethernet

TXD[3:0]

2.5-V CMOS output

4

Ethernet Transmit RGMII Data Bus

TXEN

2.5-V CMOS output

1

Ethernet Transmit Enable

GTXCLK

2.5-V CMOS output

1

Ethernet Transmit Clock

Table 2–4. Stratix IV GT I/O Usage Summary (Part 4 of 5)

Function

I/O Type

I/O Count

Description