Max ii cpld epm2210 system controller, Max ii cpld epm2210 system controller –11 – Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 19

Chapter 2: Board Components

2–11

MAX II CPLD EPM2210 System Controller

September 2010

Altera Corporation

100G Development Kit, Stratix IV GT Edition Reference Manual

MAX II CPLD EPM2210 System Controller

The board utilizes the EPM2210 System Controller, an Altera MAX

II CPLD, for the

following purposes:

■

FPGA configuration from flash memory

■

Power consumption monitoring

■

Temperature monitoring

■

Virtual JTAG interface for PC-based power and temperature GUI

■

Control registers for clocks

■

Control registers for Remote System Update

■

Control registers for general purpose I/O and PFL.

■

Register with CPLD design revision and board information (read-only)

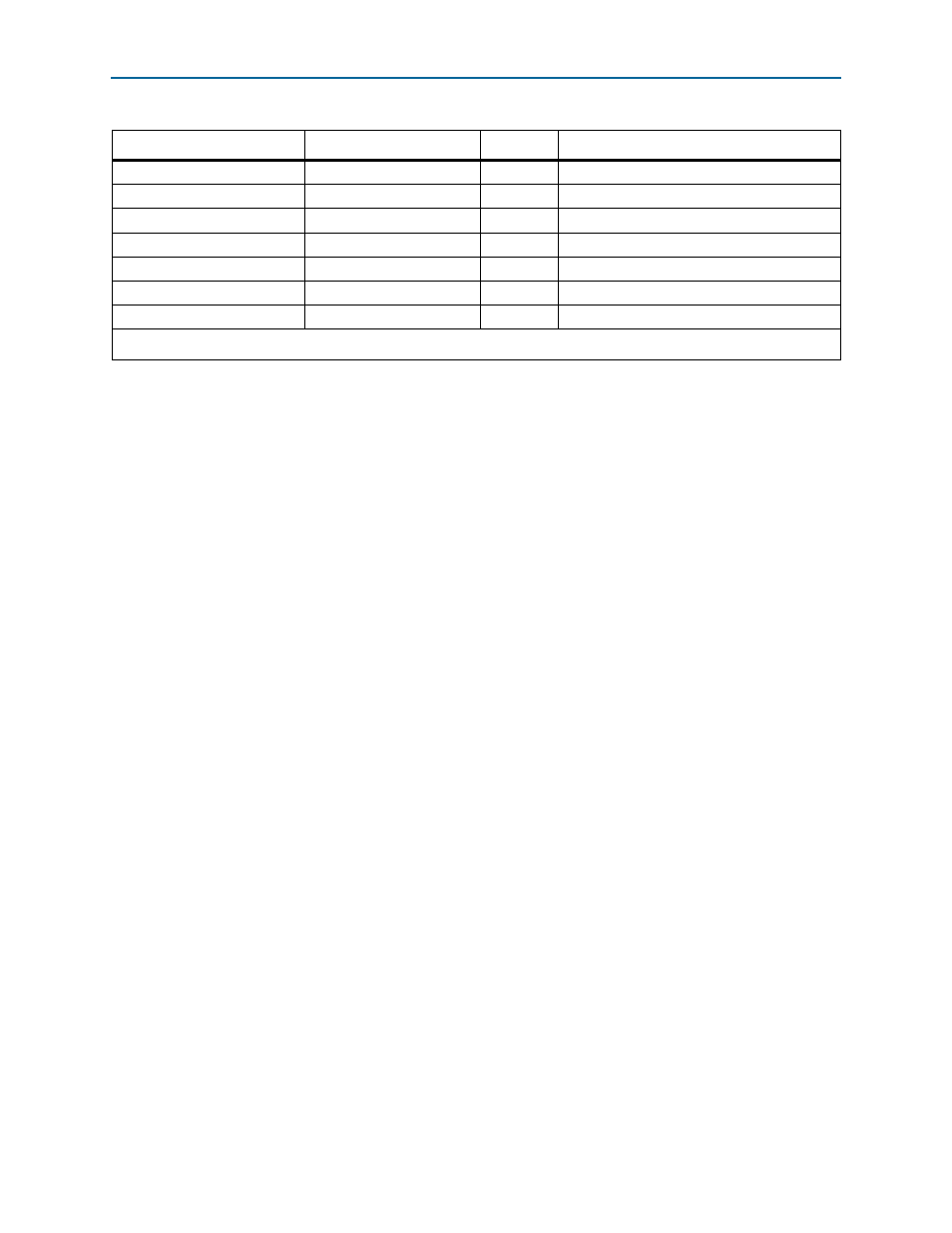

RXD[3:0]

2.5-V CMOS input

4

Ethernet Receive RGMII Data Bus

RXDV

2.5-V CMOS input

1

Receive Data Valid

RXCLK

2.5-V CMOS input

1

Receive Clock

MDC

2.5-V CMOS input

1

Ethernet MII Clock

MDIO

2.5-V CMOS bidirectional

1

Ethernet MII Data

ENET_RESET

2.5-V CMOS output

1

Ethernet reset

ENET_LED_LINK1000

2.5-V CMOS output

1

Ethernet LINK1000 LED

Device I/O Total: 916

Table 2–4. Stratix IV GT I/O Usage Summary (Part 5 of 5)

Function

I/O Type

I/O Count

Description