Sfp+ interface, Sfp+ interface –40 – Altera 100G Development Kit, Stratix IV GT Edition User Manual

Page 48

2–40

Chapter 2: Board Components

Components and Interfaces

100G Development Kit, Stratix IV GT Edition Reference Manual

September 2010

Altera Corporation

SFP+ Interface

The development board consists of two SFP+ interfaces. One SFP+ interface (SFPA)

connects to the Stratix IV GT transceivers through an electronic dispersion

compensation (EDC) chip. The EDC chip includes retimer devices which enable the

SFP+ interface to achieve 11.3-Gbps. The second SPF+ interface (SFPB) does not have

an EDC chip and connects directly to the Stratix IV GT transceivers. The SFP+

interfaces consist of one full-duplex 11.3-Gbps transceiver channel.

lists the pin assignments for the SFP+ interface (SFPA) and their

corresponding schematic signal names and Stratix IV GT pin numbers.

J34.8

Module interrupt output:

0: Possible module operational fault

1: Normal mode

QSFP_INTERUPTN

U44.M37

—

J34.7

Module present (output):

0: Module present (inserted)

1: Module absent

QSFP_MOD_PRSN

U44.M38

—

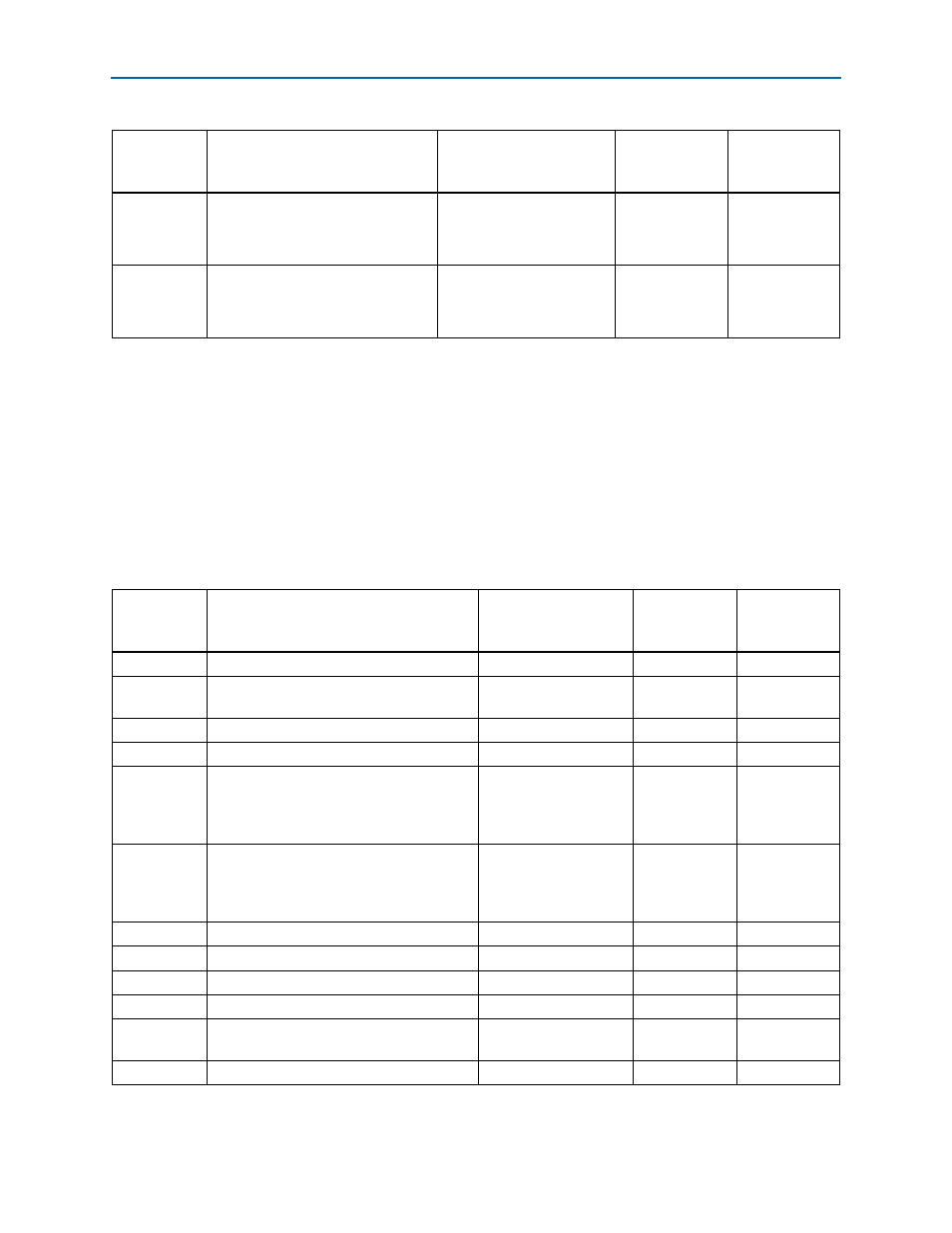

Table 2–29. QSFP Interface Pin Assignments, Schematic Signal Names, and Functions

Board

Reference

Description

Schematic

Signal Name

Stratix IV GT

Device

Pin Name

Other

Connections

Table 2–30. SFP+ Interface (SFPA) Pin Assignments, Schematic Signal Names, and Functions

Board

Reference

Description

Schematic

Signal Name

Stratix IV GT

Device

Pin Name

Other

Connections

J32.8

Signal loss indicator from the SFP+ interface

SFPA_LOS

U44.AD30

—

J32.6

Module present indicator from the SFP+

interface

SFPA_MOD0_PRSNTN

U44.AH39

—

J32.5

Two-wire serial interface clock line

SFPA_MOD1_SCL

U44.AG39

—

J32.4

Two-wire serial interface data line

SFPA_MOD2_SDA

U44.AF39

—

J32.7

Rate select 0. Controls the SFP+ interface

receiver. When input signaling is high, the

rate is > 4.25 GBps and when input signaling

is low, the rate

4.25 GBps.

SFPA_RATESEL0

U44.AE30

—

J32.9

Rate select 1. Controls the SFP+ interface

transmitter. When input signaling is high,

the rate is > 4.25 GBps and when input

signaling is low, the rate

4.25 GBps.

SFPA_RATESEL1

U44.AE31

—

J32.12

Received data (output from SFP+ interface)

SFPA_RXN

—

EDC

J32.13

Received data (output from SFP+ interface)

SFPA_RXP

—

EDC

J32.19

Transmitted data (input to SFP+ interface)

SFPA_TXN

—

EDC

J32.18

Transmitted data (input to SFP+ interface)

SFPA_TXP

—

EDC

J32.3

Turns off and disables the transmitter laser

output

SFPA_TXDISABLE

U44.AG38

—

J32.2

Interface transmitter fault

SFPA_TXFAULT

U44.AD29

—