Interrupt priority register initialization – Zilog Z86193 User Manual

Page 107

Z8

®

CPU

User Manual

UM001604-0108

Interrupts

100

Interrupt Priority Register Initialization

The Interrupt Priority Register (IPR) displayed in

is a write-only register that

sets priorities for the vectored interrupts in order to resolve simultaneous interrupt

requests. (There are 48 sequence possibilities for interrupts.) The six interrupt levels

IRQ0-IRQ5 are divided into three groups of two interrupt requests each. One group con-

tains IRQ3 and IRQ5. The second group contains IRQ0 and IRQ2, while the third group

contains IRQ1 and IRQ4.

Priorities can be set both within and between groups as listed in

and

on page 101. Bits 1, 2, and 5 define the priority of the individual members within

the three groups. Bits 0, 3, and 4 are encoded to define six priority orders among the three

groups. Bits 6 and 7 are reserved.

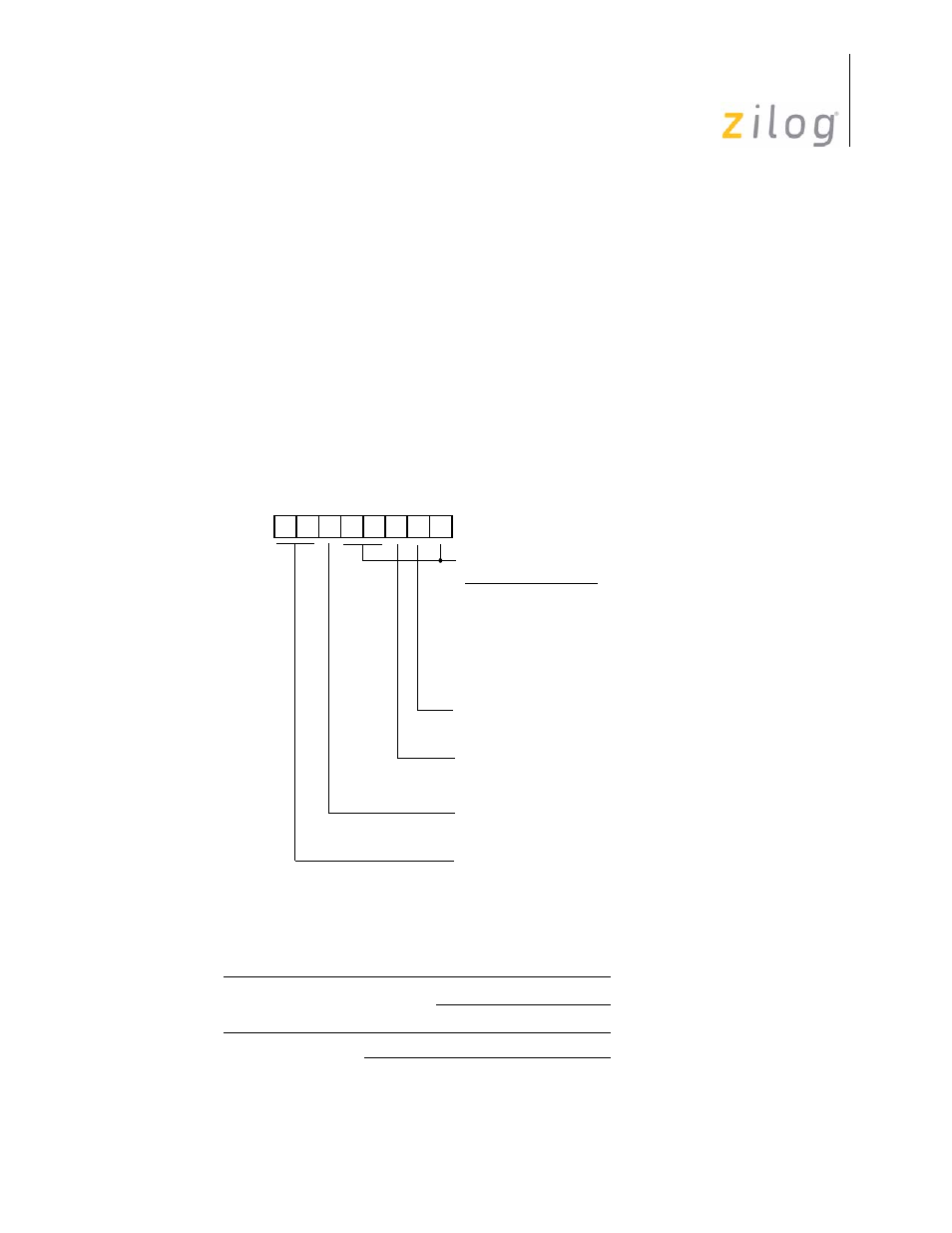

Figure 96. Interrupt Priority Register

Table 19. Interrupt Priority

Group

Bit

Value

Priority

Highest

Lowest

C

Bit 1

0

IRQ1

IRQ4

1

IRQ4

IRQ1

D7 D6 D5 D4 D3 D2 D1 D0

(Write-Only)

Interrupt Priority Register (IPR)

Register F9h

Interrupt Group Priority

Bits Priority

000 Reserved

001 C > A > B

010 A > B > C

011 A > C > B

100 B > C > A

101 C > B > A

110 B > A > C

111 Reserved

0 = IRQ1 > IRQ4

1 = IRQ4 > IRQ1

Group C (IRQ1 and IRQ4 Priority)

Reserved (Must be 0)

0 = IRQ2 > IRQ0

1 = IRQ0 > IRQ2

Group B (IRQ0 and IRQ2 Priority)

0 = IRQ5 > IRQ3

1 = IRQ3 > IRQ5

Group A (IRQ3 and IRQ5 Priority)

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003