Vectored interrupt cycle timing, Figure 101 – Zilog Z86193 User Manual

Page 114

Z8

®

CPU

User Manual

UM001604-0108

Interrupts

107

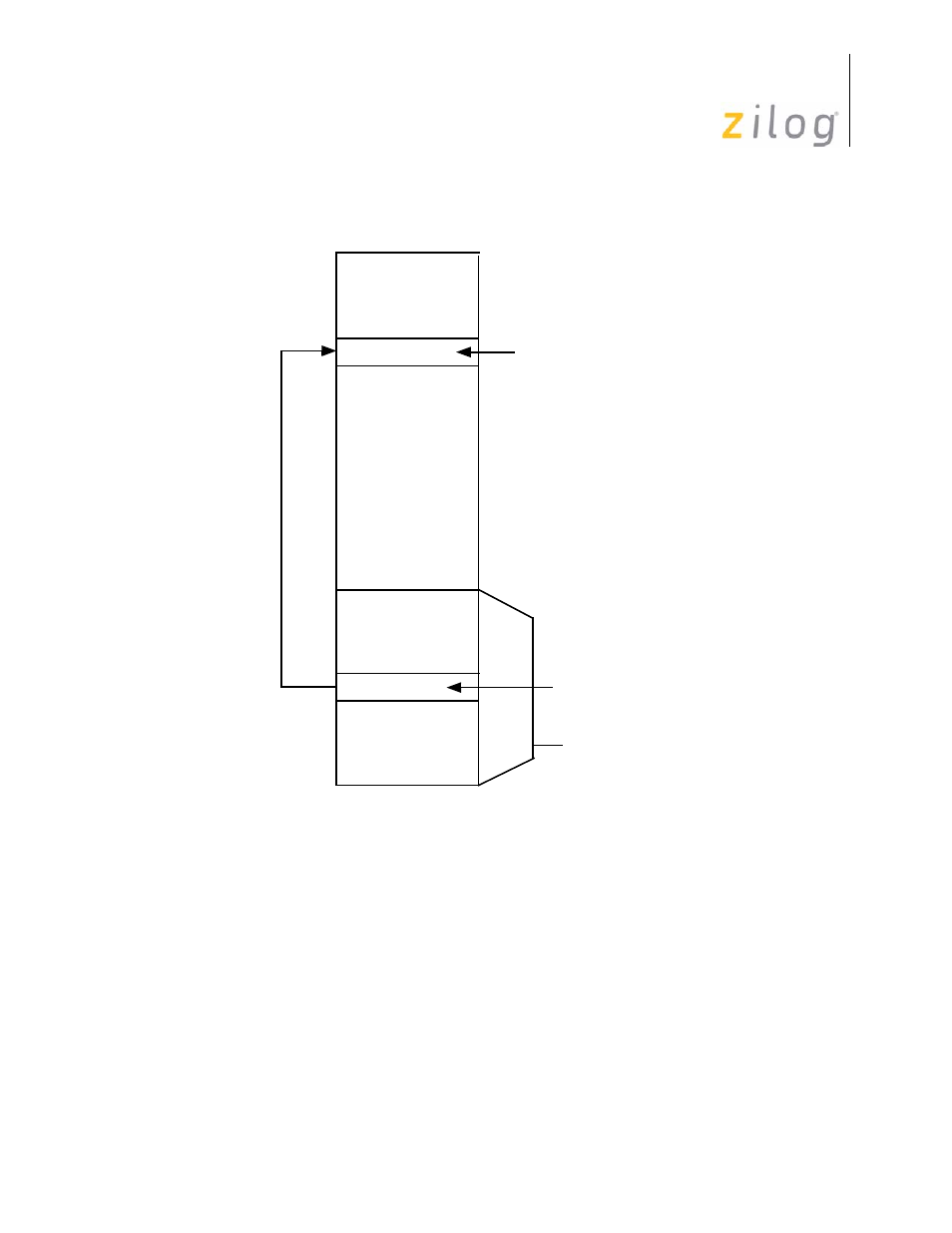

Vectored Interrupt Cycle Timing

The interrupt acknowledge cycle time is 24 internal clock cycles and is displayed in

on page 108. In addition, two internal clock cycles are required for the syn-

chronizing flip-flops. The maximum interrupt recognition time is equal to the number of

clock cycles required for the longest executing instruction present in the user program

(assumes worst case condition of interrupt sampling,

on page 99, just prior to

the interrupt occurrence). To calculate the worst case interrupt latency (maximum time

required from interrupt generation to fetch of the first instruction of the interrupt service

routine), sum these components:

Worst Case Interrupt Latency

≈

24 INT CLK (interrupt acknowledge time) + # T

P

C of

Figure 101. Interrupt Vectoring

PC HIGH Byte

FLAGS

Vector Selected

000Ch

Program Memory

Interrupt

Service

Routine

By Priority Logic

Interrupt

Vector Table

0000h

XXFFh

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003