Cpu user manual, Address space, Figure 6. expanded register file architecture – Zilog Z86193 User Manual

Page 18

Z8

®

CPU

User Manual

UM001604-0108

Address Space

11

Currently, three out of the possible sixteen Z8 ERF Banks have been implemented. ERF

Bank 0, also known as the Z8

®

Standard Register File, has all 256 bytes defined, as dis-

played in

on page 12. Only Working Register Group 0 (register addresses

00h

to

0Fh

) has been defined for ERF Bank C and ERF Bank F (see

other working register groups in ERF Banks C and F, as well as the remaining thirteen

ERF Banks, are not implemented. All are reserved for future use.

*Note: The fully implemented register file is shown. Refer to the specific product specification for ac-

tual register file architecture implemented.

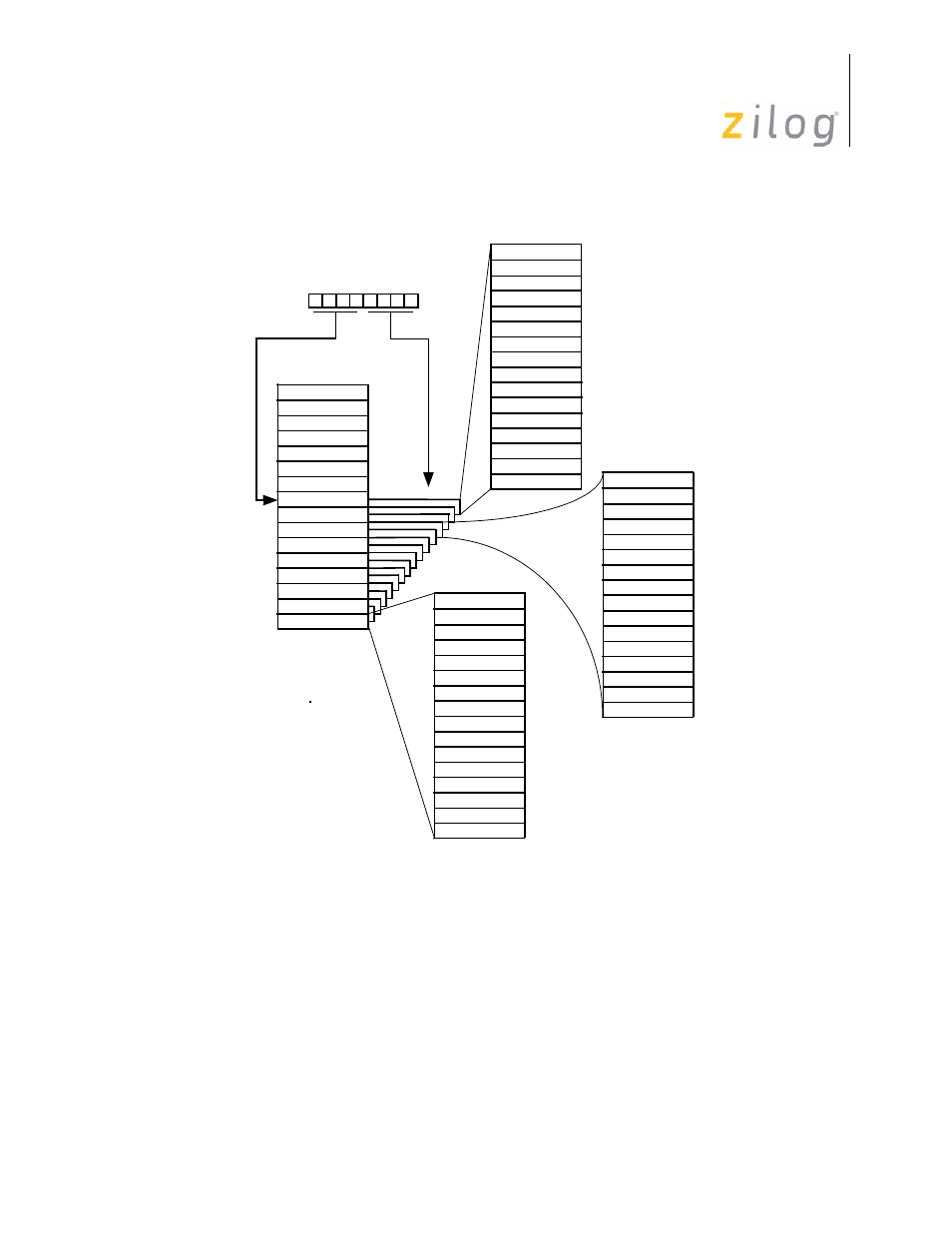

Figure 6. Expanded Register File Architecture

Z8 Register File

(F) 0F WDTMR

Expanded Register

FF

0F

7F

F0

00

Expanded Register File

Bank (F)

(F) 0E Reserved

(F) 0D Reserved

(F) 0C Reserved

(F) 0B SMR

(F) 0A Reserved

(F) 09 Reserved

(F) 08 Reserved

(F) 07 Reserved

(F) 06 Reserved

(F) 05 Reserved

(F) 04 Reserved

(F) 03 Reserved

(F) 0E Reserved

(F) 02 Reserved

(F) 01 Reserved

(F) 00 PCON

(0) 0F GPR

Expanded Register File

Bank (0)

(0) 0E GPR

(0) 0D GPR

(0) 0C GPR

(0) 0B GPR

(0) 0A GPR

(0) 09 GPR

(0) 08 GPR

(0) 07 GPR

(0) 06 GPR

(0) 05 GPR

(0) 04 GPR

(0) 03 P3

(0) 02 P2

(0) 01 P1

(0) 00 P0

(C) 0F Reserved

Expanded Register File

Bank (C)

(C) 0E Reserved

(C) 0D Reserved

(C) 0C Reserved

(C) 0B Reserved

(C) 0A Reserved

(C) 09 Reserved

(C) 08 Reserved

(C) 07 Reserved

(C) 06 Reserved

(C) 05 Reserved

(C) 04 Reserved

(C) 03 Reserved

(C) 02 SCON

(C) 01 RXBUF

(C) 00 SCOMP

D7 D6 D5 D4 D3 D2 D1 D0

Working Register

Group Pointer

Group Pointer

Register Pointer

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003