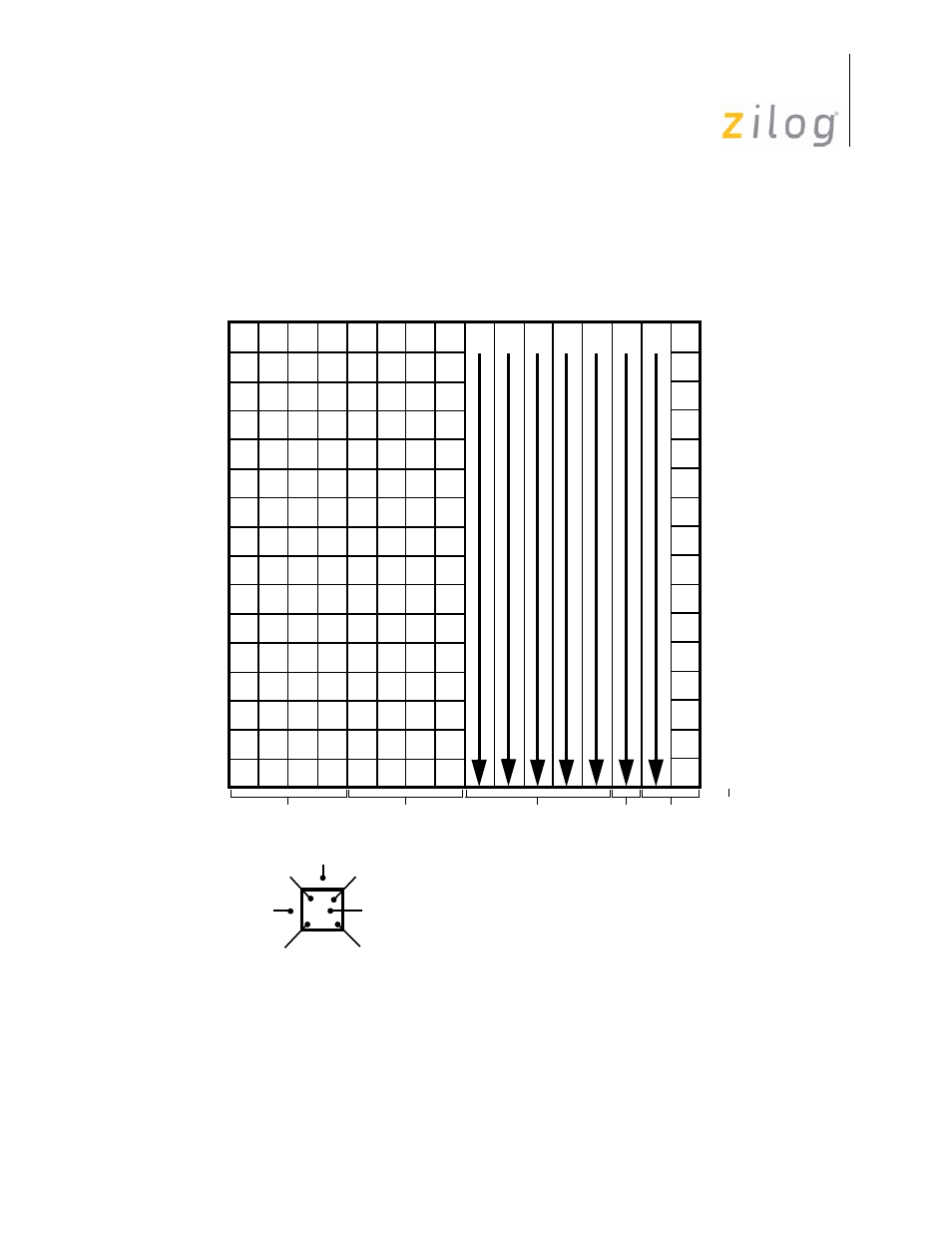

Op code map, Cpu user manual, Figure 134 displays the opcode map – Zilog Z86193 User Manual

Page 163: Instruction set, Figure 134. op code map

Z8

®

CPU

User Manual

UM001604-0108

Instruction Set

156

Op Code Map

displays the opcode map.

Figure 134. Op Code Map

10.5

CP

R , R1

6.5

DEC

R1

6.5

DEC

IR1

6.5

ADD

r1, r2

6.5

ADD

r1, Ir2

10.5

ADD

R2, R1

10.5

ADD

IR2, R1

10.5

ADD

R1, IM

10.5

ADD

IR1, IM

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Lower Nibble (Hex)

Bytes per Instruction

2

3

2

3

1

6.5

RLC

R1

6.5

RLC

IR1

6.5

ADC

r1, r2

6.5

ADC

r1, Ir2

10.5

ADC

R2, R1

10.5

ADC

IR2, R1

10.5

ADC

R1, IM

10.5

ADC

IR1, IM

6.5

INC

R1

6.5

INC

IR1

6.5

SUB

r1, r2

6.5

SUB

r1, Ir2

10.5

SUB

R2, R1

10.5

SUB

IR2, R1

10.5

SUB

R1, IM

10.5

SUB

IR1, IM

10.5

DECW

RR1

10.5

DECW

IR1

6.5

RL

R1

6.5

RL

IR1

10.5

INCW

RR1

10.5

INCW

IR1

6.5

CP

r1, r2

6.5

CP

r1, Ir2

10.5

CP

R2, R1

10.5

CP

IR2, R1

10.5

CP

R1, IM

10.5

CP

IR1, IM

6.5

CLR

R1

6.5

CLR

IR1

6.5

XOR

r1, r2

6.5

XOR

r1, Ir2

10.5

XOR

R2, R1

10.5

XOR

IR2, R1

10.5

XOR

R1, IM

10.5

XOR

IR1, IM

6.5

RRC

R1

6.5

RRC

IR1

12.0

LDC

r1, Irr2

18.0

LDCI

Ir1, Irr2

10.5

LD

r1,x,R2

6.5

SRA

R1

6.5

SRA

IR1

20.0

CALL*

IRR1

20.0

CALL

DA

10.5

LD

r2,x,R1

6.5

RR

R1

6.5

RR

IR1

6.5

LD

r1, IR2

10.5

LD

R2, R1

10.5

LD

IR2, R1

10.5

LD

R1, IM

10.5

LD

IR1, IM

8.5

SWAP

R1

8.5

SWAP

IR1

6.5

LD

Ir1, r2

10.5

LD

R2, IR1

6.5

LD

r1, R2

6.5

LD

r2, R1

12/10.5

DJNZ

r1, RA

12/10.0

JR

cc, RA

6.5

LD

r1, IM

12.10.0

JP

cc, DA

6.5

INC

r1

6.0

STOP

7.0

HALT

6.1

DI

6.1

EI

14.0

RET

16.0

IRET

6.5

RCF

6.5

SCF

6.5

CCF

6.0

NOP

2

4

A

Lower

Op Code

Nibble

Pipeline

Cycles

Mnemonic

Second

Operand

Fetch

Cycles

Upper

Op Code

Nibble

First

Operand

Legend:

R = 8-Bit Addr ess

r = 4-Bit Addr ess

R1 or r1 = Dst Addr ess

R2 or r2 = Src Address

Sequence:

Opcode, First Operand,

Second Operand

Note: Blank areas are reserved.

*2-byte instruction appears as

a 3-byte instruction

8.0

JP

IRR1

6.1

SRP

IM

6.5

SBC

r1, r2

6.5

SBC

r1, Ir2

10.5

SBC

R2, R1

10.5

SBC

IR2, R1

10.5

SBC

R1, IM

10.5

SBC

IR1, IM

8.5

DA

R1

8.5

DA

IR1

6.5

OR

r1, r2

6.5

OR

r1, Ir2

10.5

OR

R2, R1

10.5

OR

IR2, R1

10.5

OR

R1, IM

10.5

OR

IR1, IM

10.5

POP

R1

10.5

POP

IR1

6.5

AND

r1, r2

6.5

AND

r1, Ir2

10.5

AND

R2, R1

10.5

AND

IR2, R1

10.5

AND

R1, IM

10.5

AND

IR1, IM

6.5

COM

R1

6.5

COM

IR1

6.5

TCM

r1, r2

6.5

TCM

r1, Ir2

10.5

TCM

R2, R1

10.5

TCM

IR2, R1

10.5

TCM

R1, IM

10.5

TCM

IR1, IM

10/12.1

PUSH

R2

12/14.1

PUSH

IR2

6.5

TM

r1, r2

6.5

TM

r1, Ir2

10.5

TM

R2, R1

10.5

TM

IR2, R1

10.5

TM

R1, IM

10.5

TM

IR1, IM

6.0

WDT

6.0

WDh

Upp

er

Ni

b

b

le

(

H

ex

)

12.0

LDC

lrr1, r2

18.0

LDCI

lrr1, Ir2

12.0

LDE

r1, lrr2

18.0

LDEI

lr1, lrr2

12.0

LDE

r2, lrr1

18.0

LDEI

lr2, lrr1

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003